# Performance and accuracy of hardware-oriented native-, emulated- and mixed-precision solvers in FEM simulations

DOMINIK GÖDDEKE\*† ROBERT STRZODKA‡ and STEFAN TUREK†

†Universität Dortmund, Fachbereich Mathematik, Vogelpothsweg 87,

44 227 Dortmund, Germany

‡ Stanford University, Max Planck Center, 353 Serra Street,

Stanford, CA 94305, USA

(submitted Dec'05, revised Jul'06, accepted Sep'06)

In this survey paper, we compare native double precision solvers with emulated- and mixed- precision solvers of linear systems of equations as they typically arise in finite element discretisations. The emulation utilises two single float numbers to achieve higher precision, while the mixed precision iterative refinement computes residuals and updates the solution vector in double precision but solves the residual systems in single precision. Both techniques have been known since the 1960s, but little attention has been devoted to their performance aspects. Motivated by changing paradigms in processor technology and the emergence of highly parallel devices with outstanding single float performance, we adapt the emulation and mixed precision techniques to coupled hardware configurations, where the parallel devices serve as scientific co-processors. The performance advantages are examined with respect to speedups over a native double precision implementation (time aspect) and reduced area requirements for a chip (space aspect).

The paper begins with an overview of the theoretical background, algorithmic approaches and suitable hardware architectures. We then employ several conjugate gradient and multigrid solvers and study their behaviour for different parameter settings of the iterative refinement technique. Concrete speedup factors are evaluated on the coupled hardware configuration of a general-purpose CPU and a graphics processor. The dual performance aspect of potential area savings is assessed on a field programmable gate array. In the last part, we test the applicability of the proposed mixed precision schemes with ill-conditioned matrices. We conclude that the mixed precision approach works very well with the parallel co-processors gaining speedup factors of four to five, and area savings of three to four, while maintaining the same accuracy as a reference solver executing everything in double precision.

Keywords: Mixed precision iterative refinement; Emulated precision; Graphics hardware; Reconfigurable hardware; Large sparse linear equation systems; FEM

$<sup>{\</sup>rm *Corresponding~author.~Email:~dominik.goeddeke@math.uni-dortmund.de}$

#### 1 Introduction

After a long period of steady growth, desktop computer architecture has reached a turning point. Further progress is no longer enabled by growth in core clock rates, but by growth in parallelism. Physical limitations, in particular thermal restrictions, generate a trend towards more parallelism on a chip: Double-core processors are already on sale and multi-core processors with much more parallelism are in the making. The parallel arrangements distribute the heat more evenly, avoiding dangerous hot spots.

In the attempt to uphold a simple sequential programming model, the CPU has only recently opted for the parallelisation instead of enhancement of its inner structures. Other more application specific chips have followed this path from the beginning. For instance, Field Programmable Gate Arrays (FPGAs) and Graphics Processor Units (GPUs) are made up of a large number of boolean or arithmetic processing elements (PEs). In these highly parallel architectures the PEs consume a high percentage of the overall transistor count, in contrast to the cache-dominated general purpose CPUs. If we use the PEs for floating point computations then the required precision has a strong impact on the size and costs of the chip. Hardwired PEs in most highly parallel architectures are therefore only single precision (e.g. in the GPU), while reconfigurable architectures (e.g. FPGA) can be configured for double precision operations, but these arithmetic units consume so many resources that efficient parallelisation is only possible with low precision units.

For memory dominated processors the change from low precision to high precision PEs has only a small impact on the overall number of transistors and thus CPUs can more easily afford to compute in high precision in the Floating Point Unit (FPU) than other more parallel devices. However, higher precision FPUs not only increase the transistor count but also require wider data paths through the chip and make it more difficult to meet timing constraints. So even the CPU would waste too many resources by concentrating on double precision alone, and the SSE units in CPUs include a dedicated optimisation for the single float format, enabling the processing of twice as many operations on single than on double floats.

We see that current hardware architectures offer a lot of computation power in single float precision but scientific applications do not take advantage of these capabilities, as the accuracy requirements apparently force them to use double precision operations exclusively. In fact, for many problems the restriction of the *computational precision* to single float would mean an unacceptable loss of the *result accuracy*, see for example the PDE case in section 5.3. The many parallel single precision PEs can be exploited by emulating high precision operations and for a completely general algorithm this is the only possibility to gain more accuracy with low precision PEs. However, for many algorithms we

do not require high precision arithmetic for all intermediate computations to gain highly accurate final results. The knowledge about the error propagation in the algorithm can be used to confine the use of high precision computations to only few relevant places. We obtain a *mixed precision method* which utilises low and high precision computations in different parts of the algorithms.

Given these three approaches of native high precision, emulated high precision and mixed precision implementations, we compare the resulting performance and accuracy in this paper. The main focus lies on the mixed precision technique for the solution of PDEs. The performance aspect is studied in view of the existing parallel co-processors that execute single precision operations extremely fast. The accuracy is examined with respect to wide applicability of these approaches for problems of high condition.

### 1.1 Mixed precision

The idea behind mixed precision methods is obviously to perform a *large* part of the computation in low and only a small part in high precision, thus allowing the hardware to save on transistors by offering many low precision and only few high precision PEs. The low and high precision PEs may reside in different chips, e.g. a general purpose CPU with double float arithmetic and a parallel co-processor with single float arithmetic. Section 4 discusses available architectures that are particularly suitable for this kind of processing.

This simple idea of utilising different precision formats in the same algorithm has surprisingly many beneficial properties:

#### Accuracy

- For many algorithms the mixed precision method can obtain exactly the same final accuracy as though the entire computation were performed in the high precision format.

- For certain algorithms, like the solution of a linear equation system, the above savings are particularly large, because even 99% of the operations can be performed in the low precision format, without affecting the final accuracy.

- Since we use less precision in the computation it is always possible to construct problems for which the mixed precision approach must break down, however, we show that even for very badly conditioned practical cases of PDE problems there is no loss in accuracy.

### Computation

• The number of transistors required to implement a hardware multiplier grows quadratically with the size of the operands (bit length). Consequently, instead of one high precision multiplier we can use the same number of transistors for four low precision multipliers if the low preci-

sion format is half the size of the high precision format.

- As a consequence of the above, the number of operations required in the emulation of a high precision format with low precision arithmetic grows quadratically with the quotient of the high and low precision number format sizes. For floating point operations even more emulation operations are required, because of the special treatment of the exponent.

- Mixed precision techniques are used extensively in reconfigurable architectures where low precision PEs directly translate into low resource consumption and thus more parallelism. In this case PEs of different precision can be configured on the same chip.

- Hardwired processors gain even more from mixed precision algorithms, because hardwired PEs are far more transistor efficient than reconfigurable ones. Thus we may utilise a highly parallel low precision co-processor for the majority of the computations and upgrade the accuracy with few high precision computations on a slower general purpose processor.

- The decision to produce a highly parallel architecture of limited precision does not limit the accuracy of the final results. In combination with a general purpose processor which supports various number formats and can emulate even more, the same parallel architecture can be used to obtain double, extended or even variable accuracy results.

### Memory

- The use of low precision formats does not only require fewer resources for the PEs but also for the memory. This is particularly important for the very expensive and limited memory that resides next to the PEs (register file, L1 cache) and the second level memory on the same die (embedded memory, L2 cache). For optimal processing, large data sets are often split into blocks that match the size of these local memories. Smaller data formats allow the division into larger blocks which increases the efficiency of the entire algorithm.

- The use of low precision formats reduces the bandwidth requirement in computations. This is much in favour of mixed precision methods as memory transfers are often the bottleneck in computations and also account for more power consumption than the computation itself.

In summary, we can say that mixed precision methods have wide applicability and benefit both computation and bandwidth limited algorithms. For bandwidth limited algorithms with low arithmetic intensity (ratio of operations per memory access), we measure almost the theoretical factor of two in speedup when transitioning from double to single float precision. More generally, in the exponential development of computer technology in the last ten years we observe that memory performance is increasing much slower than computational performance, because the integration of additional PEs into

a processor is much cheaper both in costs and power than the widening of the data bus for additional bandwidth. This leads to the so-called *memory* wall [1], the inability to provide enough bandwidth for the PEs, thus limiting the overall performance of the system by the memory performance rather than the peak computational performance. Using low precision number formats in most intermediate computations of an algorithm cuts the bandwidth requirements almost in half and thus alleviates the memory wall problem.

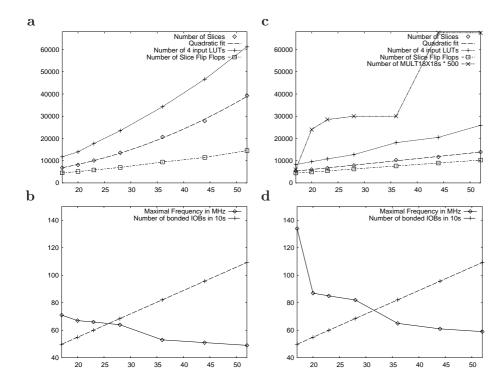

If a particular algorithm is computation limited despite the general memory wall problem, then the savings obtained from mixed precision methods can be even larger than in the memory limited case, since the area of a multiplier grows quadratically with the bit length of the operands. Thus, cutting the number format size in half allows up to four times as many PEs on the same area. The factor is not exactly four, as there is some overhead associated with each unit and for floating point numbers the ratio of the exponent to the mantissa has additional impact. Also, in hardwired architectures this quadratic advantage cannot be exploited so easily since the data paths are fixed. Therefore, hardwired dual-mode FPUs, like the SSE unit in current CPUs, have only a linear and not quadratic efficiency, offering twice and not four times as many operations in single than double precision. In reconfigurable architectures where we have control over the data paths, we do indeed benefit directly from the quadratic savings and can configure four single instead of one double multiplier, see section 7.

To avoid the inefficiency of dual-mode FPUs we could think of producing chips with four times as many single float units and emulate double precision when needed. However, once a chip has been fabricated with single precision FPUs, emulation of double precision costs much more than the factor of four, because we are confined to a fixed instruction set and cannot use the transistors in the most efficient way for the emulation, see section 2.2. Thus, we are in a dilemma: a dual-mode FPU offers only two instead of four single precision operations. However, if the same transistors are invested in four single precision FPUs, we double the single precision performance, but also half or even quarter double precision performance due to the inefficient emulations. To resolve this problem the chips simply concentrate on the precision that is most often used in their application domains and take into account that operations in the other precision will be fairly inefficient in comparison to the other architecture. With mixed precision methods we actually take advantage of this specialisation for a certain precision and divide the algorithm into two parts that execute best on one or the other architecture, see section 3.

In reconfigurable hardware the tradeoff between the precision and area of a multiplier is truly quadratic, but here we pay a price a-priori, as the area of a configured FPU is approximately six times larger than that of a hardwired FPU. This is the reason why newer FPGAs contain hardwired integer multipliers in high numbers. They can be efficiently used for the treatment of the mantissa of floating point numbers. Integer multipliers have the advantage of allowing efficient emulations of higher precision integer operations, see section 2.2. But even with embedded hardwired multipliers there still remains a configuration overhead for the data paths. The optimal balance between hardwired and reconfigurable elements, in particular for floating point operations, is discussed in detail by Ho et al. [2].

### 1.2 Paper organisation

The paper is roughly divided in four parts. After this introductory section, we discuss the theoretical background of high precision floating point emulation and the mixed precision iterative refinement technique in sections 2 and 3. Section 3.2 describes our general template of the iterative refinement algorithm for the solution of large, sparse linear equation systems. The next section is devoted to hardware configurations particularly suitable for the discussed algorithms. The third part of the paper contains our main numerical and benchmarking results. After a brief introduction to the test procedure that we apply in the finite element context, we present tests to analyse the performance and accuracy of the iterative refinement solvers in section 5. Section 6 then reports on achievable speedups with both the emulation and the refinement techniques using a GPU as a co-processor to the general purpose CPU. We analyse the potential resource savings on a FPGA in section 7. The last section of the paper returns to the numerical examination of the iterative refinement schemes with respect to increasingly ill-conditioned matrices. There, we employ operator and mesh anisotropies as a practical approach to examine such influences in the FEM context. We conclude with a concise summary, plans and suggestions for future work. The appendix contains tables with the actual performance and accuracy numbers, while in the main text we use mostly diagrams for better readability.

Given the combination of diverse research areas ranging from numerical analysis to hardware systems we do not present related work in one place, but rather discuss related approaches in the individual sections. This allows to discuss the techniques, their background and application to our algorithms in one context.

### 2 High precision emulation

#### 2.1 Exact and redundant emulation

For unsigned integers the emulation of higher precision arithmetic with lower precision units is straightforward. An addition of two m-bit operands generates a m+1-bit, and a multiplication a 2m-bit result. Integer units typically provide a carry bit that stores the additional bit of the sum, and subsequent assembly commands can include this carry bit in the addition, such that an arbitrary long chain of m-bit words can be processed to emulate a  $k \cdot m$ -bit format. In case of the multiplication, the hardware either provides the entire 2m-bit result of a  $m \times m$ -bit multiplication and thus the product of two  $k \cdot m$ -bit operands results from the addition of  $\frac{1}{2}k(k+1)$  mixed  $m \times m$ -bit products; or the multiplier delivers only a m-bit result, then each m-bit word must be split into two m/2-bit words and we have four times as many mixed products to process.

The emulation of higher precision floating point numbers follows the same lines, but there is an additional difficulty as the bits belonging to the exponent must be treated differently. So while an emulated  $k \cdot m$ -bit integer has exactly the same precision as a native  $k \cdot m$ -bit integer (exact emulation), floating point emulations with the same property are too expensive in software due to the treatment of rounding modes, denormalisation etc. Instead, a partially redundant number representation with less precision is chosen in favour of efficiency (redundant emulation). This technique has been introduced by Møller, Knuth, Dekker and other researchers in the late 1960s [3–5]. In the literature, it is referred to with a variety of different names, double-single, nativepair arithmetic or double-length floating point. We will use the first nomenclature.

For example, if the hardware provides only s23e8 single float arithmetic, we can emulate a higher precision format by spreading the mantissa over two single float values and use the exponents to align the two mantissas. The resulting precision equivalents approximately a s46e8 format, but the effective range of the exponent is reduced by 23. In this respect the double-single format is even less precise than an exact s46e8 format and is clearly inferior to a full s52e11 IEEE double. However, the two separate exponents allow to represent some numbers, e.g.  $1+2^{-100}$ , that are rounded off even in the double format. So the comparison to a s46e8 format is only approximative.

With native double (s52e11) or extended precision (s64e15) support in current CPUs, this approach is most often used to construct higher precision formats, e.g. by combining two native double precision values into a *quad precision* format [6, 7] or even arbitrary precision [8, 9]. These approaches are applicable if the underlying floating point format satisfies certain minimal conditions, e.g. faithful rounding and the existence of guard bits.

#### 2.2 Double-single operations

Arithmetic operations on combinations of low precision floating point values require a careful treatment of overflows and underflows between the high and low order parts, using only low precision arithmetic operations. In this section, we will briefly present the algorithms for addition and multiplication. For reference implementations and more details, we refer to Bailey et al. and the GNU Multiple Precision Arithmetic Library [10, 11].

Addition of two double-single values c = a + b is straightforward. The high-order parts are added, then the low order parts are added including the error from the high order addition. Finally the overflow from the low part is included in the high part. In pseudocode (using the notation .hi and .lo for the two components), we get:

Double-single addition c = a + b, cf. [10]:

(i) Compute high-order sum and error:

```

t1 = a.hi + b.hi

e = t1 - a.hi

```

(ii) Compute low order term, including error and overflows:

```

t2 = ((b.hi - e) + (a.hi - (t1 - e))) + a.lo + b.lo

```

(iii) Normalise to get final result:

```

c.hi = t1 + t2

c.lo = t2 - (c.hi - t1)

```

We note that the emulated arithmetic for addition requires 11 native operations.

Multiplication is slightly more complicated. The emulation is significantly cheaper on systems that provide a fused multiply-add (y = a + b \* c), i.e. rounding and normalisation in the underlying floating point system are not performed until the final addition (the product b\*c is not rounded before the accumulation to a). If no fused multiply-add is available, the low and high order products during the multiplication have to be split separately.

Double-single multiplication c = a \* b, cf. [10]:

- (i) Compute initial high-order approximation and error:

- If a fused multiply-add is available:

```

c11 = a.hi * b.hi

c21 = a.hi * b.hi - c11

```

• If no fused multiply-add is available:

```

cona = a.hi * 8193.0

conb = b.hi * 8193.0

a1 = cona - (cona - a.hi)

b1 = conb - (conb - b.hi)

a2 = a.hi - a1

```

```

b2 = b.hi - b1

c11 = a.hi * b.hi

c21 = (((a1 * b1 - c11) + a1 * b2) + a2 * b1) + a2 * b2

```

(ii) Compute high-order word of mixed term:

```

c2 = a.hi * b.lo + a.lo * b.hi

```

(iii) Compute (c11, c21) + c2 using Knuth's trick, including low-order product:

```

t1 = c11 + c2

e = t1 - c11

t2 = ((c2 - e) + (c11 - (t1 - e))) + c21 + a.lo * b.lo

(iv) Normalise to get final result:

```

c.hi = t1 + t2c.lo = t2 - (c.hi - t1)

We note that 18 native arithmetic operations are required, and 32 if no fused multiply-add is available.

Variations of these algorithms have been published, it is for example possible to save a few operations and trade them for an additional branch. We refer to the literature for more details [6, 9].

#### 2.3 Normalisation

Both the addition and the multiplication perform a normalisation step at the end of the computation. In an effort to reduce the instruction count in the emulation one can skip this step, thus trading performance for precision. Before normalisation the lower term t2 in the addition of two numbers a, b has an exponent of at most ExponentOf( $\max(a.hi,b.hi)$ ) -23+2. If a.hi and b.hi have the same sign, then t1 has an exponent of ExponentOf( $\max(a.hi,b.hi)$ ) or one higher, so the mantissas are already almost aligned, and we could skip the normalisation. In the worst case this leads to the loss of 2 bits of precision in a subsequent operation. However, if a.hi and b.hi have different signs, then the normalisation step is much more important, as the exponent of t1 can greatly vary. In the worst case t1 evaluates to zero and the normalisation step is crucial to transfer the mantissa from the lower to the upper term. In multiplications we are generally on the safe side, since the high order term a.hi \* b.hi dominates the result and thus its exponent.

The general effect of fewer normalisations is an increase of the redundancy of the format, because now we allow for a double-single c that ExponentOf(c.lo) > ExponentOf(c.hi) - 23. This is just a specific example of the general tradeoff between the latency of operations and the redundancy of the operand representation in arithmetic hardware circuits.

### 3 Mixed precision iterative refinement

### 3.1 Background and related work

Iterative refinement methods have been known for more than 100 years already. They gained rapid interest with the arrival of computer systems in the 1940s and 1950s. Wilkinson et al. [12–14] combined the approach with accumulated inner products as a means to assess and increase the accuracy of computed results for linear system solvers, and provided a solid theoretical foundation of these methods. The core idea is to use the residual of a computed solution as a right hand side to solve a correction equation. This process is iterated, and it is essential that the residuals are computed with higher than working precision (see below). The algorithm in its original form to solve  $\mathbf{A}\mathbf{x} = \mathbf{b}$  for a quadratic  $N \times N$  matrix  $\mathbf{A}$  reads:

$$m{x}^{(0)} = 0$$

$m{d}^{(s)} = m{b} - m{A} m{x}^{(s)}$  compute residual in  $high$  precision

$m{A} m{c}^{(s)} = m{d}^{(s)}$  solve equation system in  $low$  precision

$m{x}^{(s+1)} = m{x}^{(s)} + m{c}^{(s)}$  accumulate solution in  $high$  precision

Wilkinson and his colleagues showed that the computed solution  $\mathbf{x}^{(s^{\star})}$  is the exact solution of  $(\mathbf{A} + \delta \mathbf{A})\mathbf{x} = \mathbf{b}$  where  $\delta \mathbf{A}$  is dependent on  $\mathbf{b}$  and uniformly bounded. The upper bound m of  $||\delta \mathbf{A}||_2$  depends on the details of the floating point system used, in particular on the intermediate rounding modes of accumulations.  $\mathbf{A}$  is 'too ill-conditioned' [13] for the precision of the computation if  $m||\mathbf{A}^{-1}||_2 \geq 1$ . In this case  $\mathbf{A} + \delta \mathbf{A}$  could be singular in the given floating point system and no solution can be obtained. If however  $m||\mathbf{A}^{-1}||_2 = 2^{-p}$  for some p > 1, then the successive iterates  $\mathbf{x}^{(s)}$  of the refinement process satisfy ( $\mathbf{x}$  denoting the exact solution):

$$||\boldsymbol{x} - \boldsymbol{x}^{(s+1)}||_2 \le \frac{2^{-p}}{1 - 2^{-p}}||\boldsymbol{x} - \boldsymbol{x}^{(s)}||_2,$$

and the refinement procedure converges to working accuracy.

They also suggest the use of a LU decomposition to solve the system quickly given multiple right hand sides. But the procedure in itself is very general and can in principle be used with any solver, especially iterative ones for large sparse matrices.

A lot of research efforts have been devoted to improve this method, and in the following, we will briefly explain selected approaches that are relevant for the context of this paper. For a more comprehensive overview and references, see Demmel et al. and Zielke and Drygalla [15, 16].

Turner and Walker [17] analyse the applicability of the iterative solver GM-RES(m) in the context of iterative refinement methods and conclude that they can achieve the same accuracy as a reference double precision solver with roughly the same arithmetic work. The original GMRES(m) solver already involves restarts and is therefore particularly well suited for the interleaving of low precision computations with few high precision corrections. The numerical examples in their publication are based on discretised linear elliptic PDEs and the scheme is implemented in FISHPACK and achieves noteworthy speedup factors.

Geddes and Zheng [18] propose a mixed precision linear Newton iteration. They demonstrate their method for a wide range of different problems such as least-squares fits of overdetermined systems and the solution of multivariate nonlinear polynomial equations. For each specialised adaptation of their algorithm, they provide a detailed cost analysis and thorough numerical tests. This work, in particular, demonstrates that the algorithmic mixed precision optimisation can be successfully applied to various problems.

Langou et al. [19] evaluate iterative refinement techniques for dense matrices on a wide variety of modern CPUs such as the Opteron, Itanium, Cray, PowerPC and Cell processors. The speedup is achieved by executing the most expensive operation, namely the LU decomposition, in lower precision. The decomposition can be computed much faster in single than in double precision and dominates the solution time with  $\mathcal{O}(N^3)$  arithmetic work. Once the LU decomposition is available, few iterations of the iterative refinement scheme (each requiring only  $\mathcal{O}(N^2)$  work) suffice to solve the problem. Adapting results from Stewart [20] the authors provide a convergence condition with an upper bound for the number of required iterations, which depends on the low and high precision bit length and the matrix condition. More general error analysis of fixed and mixed precision iterative refinement techniques is provided by Stewart and Higham [20, 21].

### 3.2 Mixed precision iterative refinement algorithm framework

In the following we describe a mixed precision iterative refinement algorithm for the large sparse linear equation systems arising in FEM simulations. In particular, it is not feasible to apply an LU decomposition or similar direct methods in this context.

The core idea of the algorithm is to split the solution process into a computationally intensive but less precise inner iteration and a computationally simple but precise outer correction loop. The loops are coupled by a scaling heuristics to enlarge the exponent range locally and consequently the dynamic range of the scheme as a whole. To solve the defect equation, an arbitrary iter-

ative solver running in low precision can be employed. In our implementation and numerical tests, we make use of conjugate gradient and multigrid solvers (cf. section 5.1).

Another view on this scheme is to interpret the inner solver as a black-box preconditioner ensuring the reduction of residuals by a prescribed number of digits for an outer Richardson iteration. Other outer solvers are of course conceivable, for example a multigrid or a BiCGStab iteration.

Let  $\varepsilon_{\text{inner}}$  and  $\varepsilon_{\text{outer}}$  denote the stopping criteria for the inner and outer solver and  $\mathbf{A}x = \mathbf{b}$  the linear equation system to be solved in high precision. Furthermore,  $\alpha$  and  $d^0$  are two scalars used for scaling and convergence control. Defect and iteration vectors are labelled  $\mathbf{d}$  and  $\mathbf{c}$  respectively. Subscript low and high indicate the precision of the data vectors. The conversion between the two precision formats is intentionally left abstract, the details depend on the target hardware: On some systems, the conversion might mean duplicating the values into a new array with different precision, on other systems, the values can be casted on the fly when they are first accessed. In any case, no special operations are performed apart from a regular number format conversion. The template form of the algorithm can then be written as:

General template of the mixed precision iterative refinement solver. Input: System matrix  $\mathbf{A}_{\text{high}}$ , right hand side  $\mathbf{b}_{\text{high}}$ , convergence parameters  $\varepsilon_{\text{inner}}$  and  $\varepsilon_{\text{outer}}$ . Output: Solution  $\mathbf{x}_{\text{high}}$ .

(i) Set initial values and calculate initial defect:

```

lpha_{

m high} = 1.0, \ m{x}_{

m high} = {

m initial \ guess}, \ m{d}_{

m high} = m{b}_{

m high} - m{A}_{

m high} m{x}_{

m high}, \ m{d}_{

m high}^0 = ||m{d}_{

m high}||.

```

(ii) Set initial values for inner solver and convert data to low precision:

$$\mathbf{A}_{\mathrm{low}} = \mathbf{A}_{\mathrm{high}}, \ d_{\mathrm{low}} = d_{\mathrm{high}}, \ c_{\mathrm{low}} = \mathrm{initial} \ \mathrm{guess}, \ d_{\mathrm{low}}^0 = ||d_{\mathrm{low}} - \mathbf{A}_{\mathrm{low}}c_{\mathrm{low}}||.$$

- (iii) Iterate inner solver until  $||d_{\text{low}} \mathbf{A}_{\text{low}} \mathbf{c}_{\text{low}}|| < \varepsilon_{\text{inner}} \cdot d_{\text{low}}^0$

- (iv) Update outer solution:  $x_{\text{high}} = x_{\text{high}} + \alpha_{\text{high}} c_{\text{low}}$ .

- (v) Calculate defect in high precision:  $d_{\text{high}} = b_{\text{high}} \mathbf{A}_{\text{high}} x_{\text{high}}$ .

- (vi) Calculate norm of defect:  $\alpha_{\text{high}} = ||\boldsymbol{d}_{\text{high}}||$ .

- (vii) Check for convergence  $(\alpha_{\text{high}} < \varepsilon_{\text{outer}} \cdot d_{\text{high}}^0)$ ; otherwise scale defect:  $d_{\text{high}} = \frac{1}{\alpha_{\text{high}}} d_{\text{high}}$  and continue with step (ii).

Note that in high precision, we only need to assemble the system once and perform a matrix-vector multiplication, a vector update and a norm calculation in each outer iteration.

Since the matrix is assembled in high precision, we gain two additional advantages: First, in the hardware-oriented scenario that we target with this work, we need the final solution in high precision on the CPU to incorporate

it in the main application (cf. sections 4 and 8.1). Second, although some systems can be represented in low precision, they cannot be assembled therein. For instance, the transformation to the reference element used in certain FEM implementations suffers strongly from cancellation effects in single precision during the computation of the Jacobi determinant for very anisotropic elements. Consequently, the approach is inapplicable if the defect equation cannot be represented in low precision at all.

As scaling heuristics, we tested both normalising the defect vector (as in the above algorithm) and shifting the exponent by multiplying with an appropriate power of two, and both work equally well.

As stopping criterion, we evaluated predefining a threshold for the (relative) reduction of the norm of the residuals by a fixed number of digits, and executing the inner solver for a fixed number of iterations. The latter has the disadvantage that eventually too many inner iterations, especially in the last step, or too frequent update steps are performed. Which of these drawbacks is more critical depends on the actual hardware, but in general an update step can be considered costly compared to a solver iteration. This is particularly true for co-processor architectures where the data bus between the different chips is comparatively slow. In our numerical experiments, we were not able to construct test cases (apart from pathological examples that are not representable in low precision) which we could not solve by iterating the inner solver until a moderate error reduction of two digits in each outer iteration was achieved. We discuss the influence of the stopping criterion further in section 5.4.

We finally note that the iterative refinement approach can be cascaded to form a multilevel mixed precision solver. Instead of solving a given problem expensively in high precision, the solution process is split up recursively into a series of defect equations which are solved in successively decreasing precision. This way, most of the arithmetic work is performed on cheap low precision PEs. The feasibility on this cascade depends on the available hardware accelerated precisions, and the minimal precision necessary to gain relative accuracy reasonably fast on a defect problem of given condition.

### 4 Acceleration scenarios

There are several parallel architectures which are particularly suitable for the mixed precision iterative refinement algorithms presented in this paper. The idea is to use the parallel low precision hardware to quickly gain relative digits of accuracy and accumulate these gains in high precision. The accumulation and the residual computation, that must be performed in high precision, may either be executed on a general purpose processor (typically the CPU of the

host system), in a more expensive high precision configuration of the parallel device, or with an emulation on the parallel device. Despite the high resource usage, a high precision configuration is preferable to the slow emulation (cf. section 2.2) and should be used if available. Therefore, we use this distinction in the following discussion of parallel co-processors, and classify them into two categories:

- S Devices that can only compute in *single* floating point precision. For the double precision computation they have to utilise the CPU or emulate them.

- SD Devices that can compute both in *single* and *double* precision. Thereby, the single performance is usually much higher than the double performance.

For one representative from each class, we give more details on the configuration for the mixed precision iterative refinement in sections 4.2 and 4.3, and present concrete implementations of a mixed precision solver and results in sections 6 and 7. The sections also examine the resulting advantages under different aspects. The evaluation of the GPU demonstrates which speedups can be achieved with this approach, the FPGA implementation concentrates on the possible resource savings assuming unchanged accuracy and performance requirements. In other words, we first examine the savings in time and then in space.

### 4.1 Parallel co-processors

This section offers a glimpse on the diversified field of parallelism on a chip. By discussing several important classes of parallel architectures along with some representatives we hope to convey the lurking possibilities of such hardware configurations in the context of mixed precision methods. Overviews of parallel computing systems, focusing especially on data-stream-based processing, are provided by Hartenstein [22, 23]. Sankaralingam et al., Guo et al. and Taylor et al. discuss the various types of parallelism and their advantages and disadvantages [24–26], and Suh et al. and Strzodka compare the performance of different parallel architectures on scientific kernels and PDE problems [27,28].

Field Programmable Gate Array (FPGA). FPGAs (class SD) allow to configure any hardware design and run it as though such a chip had been fabricated. This is very practical for the testing of future chips but is also widely exploited to map problem solvers into a hardware configuration, generating a processor designed specifically for the application in mind.

FPGAs have been integrated on a wide variety of boards. For use in a PC one obtains a PCI, PCI-X (PCI Extended) or PCIe (PCI Express) board with one or more FPGAs and usually additional local memory and a micro-controller. There exist also stand-alone FPGA boards that connect to a PC for example

via USB, but due to the low bandwidth connection these are obviously less suitable for an interleaved CPU-FPGA computation. In the mixed precision iterative refinement algorithm one can then configure the FPGA to perform many parallel low precision computations of the inner solver and accumulate the corrections on the CPU or reconfigure the FPGA for high precision computations. However, the latter option is only feasible if special configuration techniques such as partial or compressed configurations are available, minimising the configuration overhead. In case of the CPU utilisation, the overhead comes from the transportation of the data back and forth to the card, which can be large for the PCI bus, but should be much smaller on the newer PCIe bus. Systems which connect the FPGA directly to a wide system bus such as the Cray XD1 or the SGI Altix offer additional advantages concerning the available bandwidth to the parallel co-processor.

Since the FPGA allows the configuration of any number format, one can further cascade the mixed precision approach and use several different precision formats within the FPGA. In particular, it is easy to generate fused operations that apply only one rounding to the final result of a composed operation, e.g. a dot product. Large accumulators can also simply use a higher intermediate precision for better accuracy.

Processor Array / Multi-core Processor. Both terms describe chips comprising many PEs that operate in parallel. Processor arrays usually refer to architectures with simple PEs that communicate with each other directly, have a common control unit that assigns data to them, or simply share local memory for data exchange. The term multi-core processors describes architectures with more complex PEs, that often themselves contain multiple elementary PEs. Beside the registers, both classes of processors typically feature small, very fast, local PE memories and larger inter chip memory accessible from all PEs. In contrast to caches, this three-level memory hierarchy is under full control of the programmer, which enables the design of highly efficient application specific data-flow, but also significantly increases the program complexity, especially as even more memory levels may be present and the communication over a bus with the host must also be taken into account. A framework specifically dedicated to a more portable and reusable exploitation of these memory hierarchies has been presented by Fatahalian et al. [29].

The Clearspeed CSX architectures [30] are examples of processor arrays. A board with several CSX chips can be integrated into a workstation via the PCI-X bus. The PEs in the CSX architecture (class SD) support single and double precision arithmetic at basically the same speed. However in favour of a reduction of internal and external bandwidth requirements it is still more advantageous to utilise the numerous parallel PEs for single float computations and apply the iterative refinement algorithms described in this paper. Smaller

number formats also allow to fit more data words into the very restricted PE memories, which is highly beneficial for many algorithms which have to store local state in addition to the processed data streams. So there are multiple reasons for using single float arithmetic even when the peak double precision performs is equal, but the transition from a pure double precision FPU to a dual-mode FPUs costs relatively few transistors, so that in future Clearspeed might decide to offer architectures that perform twice the number of single float than double float operations.

A representative of the multi-core processors is the Cell BE processor (Sony, Toshiba, IBM) [31]. It is available as a blade server or a PCIe accelerator board for the PC [32]. The Cell BE (class SD) also offers single and double float arithmetic, but the peak single float performance is more than ten times higher than the peak double performance. In common scientific computing applications this discrepancy results in a slowdown by a factor of 5 to 20 for double precision [33]. Moreover, similar to the CSX chips, a smaller number format increases the word throughput and local storage of the PEs in the Cell BE.

The general purpose CPU is quickly developing towards a multi-core processor. After the double-core versions both Intel and AMD already announced quad-core processors for the near future. Although current CPUs still offer little parallelism in comparison to the other architectures discussed here, with the growing number of cores and a possible widening of the SSE unit the situation might change in the future.

Application specific hardware. Some application specific hardware products expose a lot of parallel PEs that are well suited for the solution of PDEs. Two examples from the world of graphics applications are the AGEIA PhysX processor [34] and modern graphics processor units (GPUs). Little is known about the internal structure of the PhysX processor. But one knows that it is a highly parallel architecture and the company claims that the computing model is particularly well suited for FEM simulations of physical phenomena. Allegedly the computation units use single float (class S?), which in view of the mixed precision methods would actually give better hardware efficiency. However, it is not clear how the data-flow for the mixed precision approach could be organised on the PhysX processor and whether a high precision emulation or corrections on the CPU were more efficient. In the latter case the low bandwidth of the connecting PCI bus could be a problem for a fast CPU-PhysX mixed precision configuration.

Modern graphics cards contain mainly one GPU and video memory. The seldom exceptions are cards that implement the different parts of the graphics pipeline in different chips rather than one GPU, and cards with two GPUs on one card. Graphics cards are connected to the PC via the AGP or the faster

PCIe bus. Most low cost GPUs are integrated directly into the chipset. GPUs offer single float computations throughout the graphics pipeline (class S). Although the numerical access to the parallel PEs is obscured by the graphics specific API, the wide availability and cost efficiency of the hardware makes them very attractive candidates for mixed precision methods. The GPU consists of independent groups of PEs. Within each group there is implicit (instruction level parallelism) and explicit data exchange (4 vector components) through registers. Above the registers GPUs have no user controllable local PE memory where local state could be stored, instead they feature dedicated cache arrangements optimised for 2D coherent memory access patterns. This means that intra group communication happens through high level memory that resides on the graphics card outside the GPU. For the GPU this implies many memory transfers to a much higher memory level than for the other architectures, including a lower bandwidth for these transfers. On large data sets the GPU can still compete with the other parallel chips, because the external bandwidth is pushed to the limit with dedicated graphics memory chips and the entire system is optimised for latency minimisation. But the lack of intermediate local memories leads more often to bandwidth bound algorithms on the GPU and considerable effort must be devoted to trading computation for bandwidth with special, often application specific algorithmic reformulations [35].

### 4.2 Graphics Processor Unit (GPU)

Since 2003 graphics processors (GPUs) offer programmable floating point arithmetic. Together with the high memory bandwidth and tremendous computational performance GPUs have emerged as powerful numerical coprocessors. A new field of research commonly called *general purpose computation on graphics hardware (GPGPU)* has evolved. We refer the reader to the survey paper by Owens et al. [36], and to the GPGPU community web site [37] for online material with introductions, paper archive, course notes, tutorial codes and further information. For a GPGPU introduction without any graphics terminology see Strzodka et al. [38].

Although GPUs are just one representative among the many powerful parallel computing devices discussed in the previous section, they attract additional attention because of their ubiquitous availability and excellent price-performance ratio. Graphics processors built into PC chipsets usually offer only very limited computational performance, but buying and installing a more powerful graphics card off the shelf is an easy and comparably inexpensive procedure. Therefore, many users would consider upgrading their GPU if they could gain significant speedups for their applications.

GPUs natively support a quasi-IEEE s23e8 floating point format which lacks

denormalisation and always rounds to zero. For a detailed analysis of the differences between the standard IEEE single precision and the format on the GPU, refer to Hillesland and Lastra [39] and Daumas et al. [40]. These differences are however minor in the context of this paper.

Da Graca and Defour analyse the applicability of double-single emulation techniques and conclude that because of faithful rounding and guard bits, the emulated precision arithmetic is well suited for GPUs [41]. Extension of this technique to complex and quad-precision numbers has been presented by Hitz and Payne [42], and a residue based number representation with variable precision is discussed by Thall [43].

The emulated high precision multiplication (cf. section 2.2) requires less instructions if a fused multiply-add operation is present. This is true for GPUs, but the composed MAD (multiply-add) instruction is not necessarily fused with respect to floating point rounding, i.e. the computed result must be the rounded exact result of the composed operation. ATI GPUs (X1K series) offer a fused multiply-add with respect to rounding, so that here the shorter emulation of the multiplication can be used, while NVIDIA GPUs (GeForce 6 and 7 series) apply intermediate rounding/truncation and thus require the longer emulation for the multiplication (according to the vendors' respective developer support).

In contrast to emulation, Dale et al. [44] suggest to equip GPUs with dual-mode PEs, realised through small-scale reconfigurability. As discussed in the introduction (cf. section 1.1), this improves double precision performance over emulation but lowers the transistor efficiency for single float arithmetic, so the decision depends on how often double precision arithmetic is indispensable for the GPU. In view of our mixed precision results (cf. section 6) we rather discourage the overall integration of double precision PEs into GPUs, as they are not needed in high numbers to achieve accurate results in PDE based physical simulations, i.e. the application area in which computer games have probably the highest demand for better accuracy. But adding some dual-mode PEs, e.g. only the moderately large double precision adders, might be useful to enable a fast execution of the high precision corrections on the GPU itself, rather than always delegating these tasks to the CPU.

The double-single emulation on the GPU is not always sufficient, as the double format has a clearly larger mantissa and exponent range than the emulated format: 52/46 = 1.13,  $2^{11}/2^8 = 8$ , and three term emulations become truly expensive. Therefore, we perform the high precision corrections on the CPU rather than emulating them on the GPU (cf. section 6). Moreover, for complex applications the corrections on the GPU do not eliminate the necessity of data transfers with the host. For complex applications it is infeasible and also unnecessary to reimplement thousands of lines of performance uncritical code on the GPU. Instead, the GPU accelerates the more regular, most demanding

parts of the algorithms, and leaves the subsequent processing of the results to the well tested, higher abstraction code on the CPU.

## 4.3 Field Programmable Gate Array (FPGA)

Hardwired processors operate on fixed-width formats and thus usually have dedicated single or double precision FPUs. They also have fixed data paths and synchronised scheduling. FPGAs have fully configurable memory and logic elements, data paths and clock generators, and thus a lot of freedom in adapting the hardware to the application.

- The input and output data formats depend on the application and not on the hardware, e.g. some imaging devices deliver data with 12 bit precision which is stored in 16-bit shorts for CPU processing.

- FPGAs are natural mixed precision processors, there is no need to utilise the same number format throughout the algorithm, or even the same operation, e.g. for a more accurate accumulation of s23e8 data we may configure a s23e8 + s36e11 → s36e11 accumulator.

- We can generate more efficient custom fused operators, e.g. redundant number representations allow to evaluate a sum of multiple addends  $\sum_i a_i$  much faster with the successive computation of b, c, such that  $b + c = a_i + a_{i+1} + a_{i+2}$ , rather than the repeated reduction  $b = a_i + a_{i+1}$ .

- There are many options to trade latency, throughput and area in operations, e.g. an  $n \times n$ -bit adder can have  $\mathcal{O}(1)$  area and  $\mathcal{O}(1/n)$  throughput or  $\mathcal{O}(n)$  area and  $\mathcal{O}(1)$  throughput.

- While FPGAs have dedicated logic and memory elements, some also have configuration elements which can be used as logic or memory. Thus additional tradeoffs between computation- and lookup-based operators are possible, e.g. a 4 input 1 output Boolean operator is realised through a 2<sup>4</sup>-bit configuration table, which can alternatively be used to store 16-bit.

- The freedom in the design of custom operators makes alternative number representations sometimes feasible on the FPGA, e.g. in the logarithmic number representation we store  $\log(a)$  instead of a and obtain the big advantage that multiplications translate into additions  $\log(a \cdot b) = \log(a) + \log(b)$ .

- All PEs operate concurrently in a FPGA, so the maximum efficiency is obtained when all PEs contribute to the solution and never stall. Thus to avoid areas with idle operators which are not required all the time, one can reuse parts of these operators in a modular design for other computations, e.g. a float adder can reuse the adder of the mantissas for integer operations.

- When reusage of a configuration is difficult because of very different operators, reconfiguration overhead can be minimised with special reconfiguration techniques, e.g. with partial reconfigurability we can replace only a part of

the circuit and thus require a much smaller configuration bitstream.

The application of these techniques from scratch requires intrinsic knowledge of a hardware description language (HDL). However, HDLs now offer many levels of abstraction and although floating point numbers are not part of the language, parameterised libraries are available [45,46]. Automatic a-priori analysis can be performed to determine the necessary precision in composed operations [47]. The tradeoffs between latency, throughput and area for floating point formats have been studied in detail [48–50]. Analysis of logarithmic number systems has also revealed under which conditions this representation is advantageous [51,52]. For more background and additional information we refer to general surveys of reconfigurable hardware presented by Bondalapati and Prasanna, and Compton and Hauck [53,54].

The above optimisations reduce the area consumption locally on the level of individual and composed operations. The mixed precision iterative refinement applied to the FPGA allows to save resources globally by reducing the precision of most intermediate operations. Although the FPGA can be configured with double precision FPUs, this consumes so many resources, that we rather use it similar to the GPU, as a fast parallel, low precision processor and perform the double precision corrections on the CPU or a micro-controller on the FPGA board. In case of the FPGA we examine the dual aspect of the reduced precision and analyse the savings in area rather than time (cf. section 7).

## 5 Test procedure and algorithmic properties

Before we present results of the proposed schemes on actual hardware configurations in the next two sections, we want to discuss several properties of the approaches in more detail and describe our test procedure in general.

#### 5.1 General test procedure

For a given test function, we solve several variants of the Poisson equation  $-\Delta u = f$  prescribing zero Dirichlet boundary conditions. Such variants of the Poisson problem are common building blocks in CFD or CSM and numerical simulation in general. For instance, projection type schemes in Navier-Stokes simulations [55] lead to Pressure-Poisson problems, often the most time-consuming step at the core of the computation (especially in non-stationary simulations). Another example are grid deformation techniques [56] that move grid points towards regions in the simulation domain with high errors, and which calculate the new positions with one Poisson problem in each deformation step.

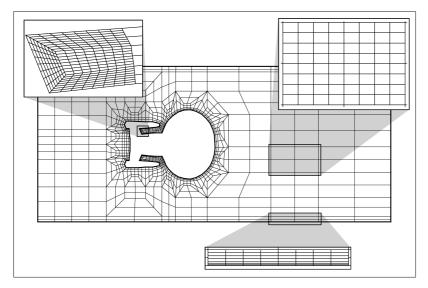

Conforming bilinear finite elements  $(Q_1)$  are used for the spatial discretisation of the exemplary domain  $\Omega = [0, X] \times [0, Y] \subseteq \mathbb{R}^2$  for different levels of refinement of an underlying generalised tensorproduct mesh, leading to problem sizes of  $N=3^2$  to  $N=1025^2$  unknowns (levels 2–10 respectively). In this section and in the discussion of actual acceleration scenarios in the following sections, all results are based on a uniform refinement of the unit square, and we do not employ a stencil but assemble the matrix fully. In section 8 we will extend the results on anisotropic discretisations and more realistic domains, but the matrix structure and hence the cost for a matrix-vector multiplication remains the same. The discretisation scheme yields a band matrix with nine bands which we store as separate vectors with appropriate zero padding.

We define a test function  $u_0: \Omega \to \mathbb{R}$  analytically as  $u_0(x,y) = x(X-x)y(Y-y)$ ,  $(x,y) \in \Omega$ . With zero Dirichlet boundary conditions, neither additional data approximation errors nor cubature errors in the right hand side are introduced which would obfuscate the accuracy issues we want to examine. The function and its analytically known derivatives are used to predefine a right hand side  $f = -\Delta u_0$ , yielding a Poisson problem with analytically known solution. During our experiments we successfully evaluated many additional test functions, but throughout this paper, we present all results based on the above test function to provide better comparability of our results.

We employ the following solvers for the numerical tests:

Conjugate gradients (CG) as an example of a basic iterative Krylov space solver. We use the standard formulation of the solver, without preconditioning or damping.

Multigrid with Jacobi smoother (MG\_JAC) as an example of a more advanced solver, capable of dealing with small grid distortions while being unbeatably fast for Cartesian meshes. We employ an F-cycle and vary the damping factor and the number of pre- and postsmoothing steps as necessary.

We compute two quality measures in each test case, the  $L_2$  error and the number of iterations until solution. The  $L_2$  error (integrated over  $\Omega$ ) of the computed solution against the analytically known reference result should behave like  $\mathcal{O}(h^2)$  (mesh width  $h = 1/\sqrt{N}$ ), yielding an error reduction factor of four in each refinement step. The conjugate gradient solver should double the amount of iterations per refinement level while the multigrid solvers should converge independent of the level.

### 5.2 Influence of the input data precision

In the first test series, we analyse the influence of the input data precision on the overall error. The right hand side for the Poisson problem is therefore

Table 1. Errors caused by reduced input data precision for a double precision solver (cf. section 5.2).

| Level | Half precision | Single precision | Double precision |

|-------|----------------|------------------|------------------|

| 8 9   | 2.333E-6       | 7.718E-10        | 2.750E-13        |

|       | 1.008E-6       | 7.726E-10        | 1.051E-12        |

precomputed in double precision as the discrete Laplacian  $\mathbf{f} = -\Delta_h \mathbf{u}_0$  to avoid discretisation errors and then truncated to double, single or half [57] float precision, while the solver itself is executed in double precision. The computed results are then compared (again in double precision) with the known reference solution. This test is performed on a uniform subdivision of the unit square. Table 1 subsumes the impact of reducing the input data precision, exemplarily for the problem sizes  $N = 257^2$  and  $N = 513^2$ .

We observe that representing all vectors in double precision is essential. Although the matrix assembly and the computation are always performed in double precision, the reduction (clamping) of the right hand side to single precision already costs approximately three digits of accuracy in the result. The furthergoing reduction to half precision costs additional three digits. In view of the targeted co-processor scenario, these results support our claim that it does not make sense to improve the internal computational precision without introducing a higher precision format for input and output.

### 5.3 Accuracy in single and double precision

In this test series, we compare how the *computational precision* in the solution process influences the *accuracy of the result*. In particular we want to emphasise the highly non-monotonic relation between them.

We perform the matrix assembly and the error calculations in double precision. The arising systems are solved in single and double precision respectively. For the solution in single precision, we cast the matrix and vectors to single precision. Table 2 lists the number of multigrid cycles, the error compared to the reference solution and the reduction factor in the error for refinement levels 2 to 10 (3<sup>2</sup> to 1025<sup>2</sup> unknowns). The stopping criterion for all tests is identically set to  $\varepsilon_{\text{outer}} = 10^{-3}$ . This threshold suffices to achieve the expected error reduction by a factor of four and thus avoids the potential accumulation of roundoff errors by performing too many inner solver iterations.

We observe that the double precision solver exhibits the expected error reduction by a factor of four per refinement. The single precision solver however does not. From levels 5 to 7, the error reduction degrades slowly to a mere factor of 1.5, and for levels 8 and 9, the error even increases again, thus wasting the additional work and memory requirements for these levels of refinement. Note that this behaviour cannot be detected based on evaluating only the

Table 2. Influence of solver precision on solution accuracy with increasing problem size (level of refinement), cf. section 5.3.

|       | s      | ingle preci | ision     | double precision |          |           |  |

|-------|--------|-------------|-----------|------------------|----------|-----------|--|

| Level | Cycles | Error       | Reduction | Cycles           | Error    | Reduction |  |

| 2     | 1      | 2.391E-3    |           | 1                | 2.391E-3 |           |  |

| 3     | 2      | 5.950E-4    | 4.02      | 2                | 5.950E-4 | 4.02      |  |

| 4     | 2      | 1.493E-4    | 3.98      | 2                | 1.493E-4 | 3.99      |  |

| 5     | 2      | 3.750E-5    | 3.98      | 2                | 3.728E-5 | 4.00      |  |

| 6     | 2      | 1.021E-5    | 3.67      | 2                | 9.304E-6 | 4.01      |  |

| 7     | 2      | 6.691E-6    | 1.53      | 2                | 2.323E-6 | 4.01      |  |

| 8     | 2      | 2.012E-5    | 0.33      | 2                | 5.801E-7 | 4.00      |  |

| 9     | 2      | 7.904E-5    | 0.25      | 2                | 1.449E-7 | 4.00      |  |

| 10    | 2      | 3.593E-4    | 0.22      | 2                | 3.626E-8 | 4.00      |  |

defects during the solution process. In both cases, the reduction rate of the residuals is identical. This is especially critical in practical scenarios where a reference solution is naturally not available. The consistent reduction of residuals on finer levels misguides one to believe that also the overall accuarcy is improved, but in fact the opposite is the case.

We examined other causes of the accuracy degradation. Neither performing more nor performing less iterations of the inner single precision solver improves the accuracy, indicating that the issue is really the lack of precision and not a side effect of accumulated roundoff errors.

In our experiments, we encountered many examples that, although performing worse from the point of view of accuracy, behaved much better from a practical point of view. For higher levels of refinement (i.e. worse matrix condition), the single precision solvers simply stopped to converge properly, which can be detected in practice by monitoring the convergence rate of the solvers.

In summary, single precision solvers for certain examples fail to gain accuracy upon further refinement. In some cases, they diverge or just slowly degrade their rate of convergence, until no further error reduction can be achieved. In other cases, instead of degrading accuracy, they increase the error again. This is especially critical as there is no straightforward means to detect this last case during the solution process.

### 5.4 Influence of the stopping criteria in iterative refinement

We evaluated two stopping criteria for the mixed precision iterative refinement algorithm, executing the inner solver for a fixed number of iterations or until the norms of the residuals have been reduced by a predefined number of digits. Our first result is quite obvious: As long as not too much work is demanded of the inner solver with respect to precision (e.g. gaining less than four digits in one outer iteration), the choice of the termination criterion does not disturb convergence or the accuracy of the final result. The latter is effectively

Table 3. Influence of the stopping criterion (cf. section 5.4). Mixed precision iterative refinement solver based on multigrid executing 1, 2 or 3 cycles (i1,i2,i3), or gaining 1,2 or 3 digits  $(\delta 1,\delta 2,\delta 3)$  in each outer iteration respectively. The column labelled 'double' lists reference values obtained in native double precision. Notation: Colon separates outer and sum of all inner iterations.

| Level | double | i1  | i2   | i3   | $\delta 1$ | $\delta 2$ | $\delta 3$ |

|-------|--------|-----|------|------|------------|------------|------------|

| 8     | 8      | 8:8 | 4:8  | 4:12 | 8:8        | 5:9        | 4:11       |

| 9     | 8      | 8:8 | 4:8  | 4:12 | 8:8        | 5:9        | 4:11       |

| 10    | 8      | 8:8 | 5:10 | 5:15 | 8:8        | 5:9        | 4:11       |

Table 4. Influence of the stopping criterion (cf. section 5.4). Mixed precision iterative refinement solver based on conjugate gradients executing 100, 250 or 500 iterations (i100, i250, i500), or gaining 1,2 or 3 digits ( $\delta$ 1,  $\delta$ 2,  $\delta$ 3) in each outer iteration respectively. The column labelled 'double' lists reference values obtained in native double precision. Notation: Colon separates outer and sum of all inner iterations.

| Level | double | i100      | i250     | i500    | $\delta 1$ | $\delta 2$ | $\delta 3$ |

|-------|--------|-----------|----------|---------|------------|------------|------------|

| 8     | 342    | 13:1300   | 4:1000   | 4:2000  | 10:1047    | 5:861      | 4:944      |

| 9     | 676    | 68:6800   | 9:2250   | 5:2500  | 10:2002    | 6:2256     | 5:2380     |

| 10    | 1357   | 264:26400 | 40:10000 | 12:6000 | 10:4504    | 6:4501     | 6:5242     |

determined by the number of *outer* iterations, which we always control by monitoring global defects in double precision.

Moreover, we experienced that the choice of the inner solver has the greatest impact on the performance of the iterative refinement scheme. In the following paragraphs, we present numerical results for both the unpreconditioned conjugate gradient solver as well as the multigrid solver with Jacobi smoother. Like all results in this section, the measurements are based on a uniform refinement of the unit square and the solver is iterated until the global residuals have been reduced by 10 digits.

Table 3 lists the number of iterations for the iterative refinement scheme using multigrid (with 2+2 Jacobi smoothing steps) as inner solver.

We observe that this type of solver only leads to a mild increase in overall iteration count, if any. A more detailed analysis of the convergence history reveals that the increase can be attributed to our choice of convergence control. When demanding too much error reduction per outer update step, it might happen that the system is not solved until the predefined ten digit reduction, but further. We conclude that the multigrid solver is very well suited to be used within a mixed precision iterative refinement solution procedure.

The conjugate gradient solver however shows an entirely different convergence behaviour, as shown in table 4. Note that the overall iteration count increases dramatically. We first assumed that this is caused by the lack of precision, namely due to roundoff errors and cancellation, subsequent steps in the algorithm fail to compute orthogonal search directions. We therefore

Table 5. Influence of the stopping criterion (cf. section 5.4). Fixed precision iterative refinement solver based on conjugate gradients executing 100, 250 or 500 iterations (i100, i250, i500), or gaining 1,2 or 3 digits ( $\delta 1, \delta 2, \delta 3$ ) in each outer iteration respectively. The inner solver uses double precision as well, and an immediate global convergence check after each inner iteration is applied. The column labelled 'double' lists reference values obtained in native double precision. Notation: Colon separates outer and sum of all inner iterations.

| Level | double | i100      | i250    | i500   | $\delta 1$ | $\delta 2$ | $\delta 3$ |

|-------|--------|-----------|---------|--------|------------|------------|------------|

| 8     | 342    | 10:970    | 2:368   | 1:342  | 10:859     | 5:673      | 4:544      |

| 9     | 676    | 66:6588   | 8:1802  | 2:763  | 10:1648    | 5:1363     | 4:1098     |

| 10    | 1357   | 261:26013 | 38:9470 | 8:3629 | 10:3472    | 5:2379     | 4:2233     |

implemented a variation of our proposed scheme, a fixed precision iterative refinement algorithm executing the inner conjugate gradient solver in double precision. To avoid distractions by performing superfluous iterations due to the less frequent convergence control of the outer solver, we also computed the global defect after each inner iteration and thus could terminate the solution process as soon as it fell below  $\varepsilon_{\text{outer}}$ .

As we see from the numbers in table 5, the lack of computational precision is only one reason for the dramatic increase in iterations. We clearly see that the conjugate gradient solver reacts very delicately to frequent restarts. The reason for it is that the conjugate gradient algorithm builds up a search space with its utility vectors, and this information is lost when the solver is restarted.

This problem can be partly alleviated by reusing the utility vectors. Obviously this is only possible if the inner solver operates always with the same right hand side, i.e. we cannot use the standard iterative refinement formulation. But the conjugate gradient algorithm already contains an accumulation of the solution vector, and therefore we can integrate the iterative refinement method directly into the core of the algorithm. The high precision correction is then performed on the residual directly and not on the solution vector, for details see the residual guided conjugate gradient variant [58]. In the limit, when the inner precision is exactly the same as the outer precision we simply obtain the original conjugate gradient algorithm. The reuse of the utility vectors is particularly helpful when the inner precision is very low (below single float) and many outer solver iterations are necessary to ensure convergence. Therefore, we have studied this variant in the context of reconfigurable hardware, where the inner precision is not limited by fixed hardware functionality but can be chosen arbitrarily [58].

### 5.5 Implementation on the CPU

Targeting the outstanding parallel compute power, we first used parallel devices for performance gains with mixed precision methods [58,59]. Recent work

of Langou et al. [19], showing speedups for a direct LU solver in the mixed precision iterative refinement setting on the CPU, encouraged us to also implement a CPU version of the mixed precision iterative solvers. However, due to the sparsity of the matrix we cannot benefit from readily available optimised BLAS and LAPACK implementations such as GotoBLAS, ATLAS or vendor-tuned packages. Benchmarking reveals that approximately 85% of the time is spend in the sparse matrix-vector multiplication, for which no BLAS or LAPACK routines are available: For the banded matrix structure and storage as individual vectors, we would require a 'saxpy\_v' operation  $(y_i = y_i + a_i x_i)$ instead of  $y_i = y_i + \alpha x_i$ ) to implement the multiplication (cf. section 5.1). Without such a SSE-optimised matrix-vector multiplication, speedups of the refinement scheme over a full double precision format are not achievable. In contrast to the direct LU solver, we would not benefit from the different complexity order of the solution steps in case of iterative solvers, but based on the iteration numbers of the schemes (cf. section 5.2) we believe that a fully optimised SSE variant would at least execute the mixed precision multigrid solver faster than a full double precision implementation.

#### 6 Solver speedups with GPUs as co-processors

We have previously published first results of the GPU-CPU mixed precision iterative refinement algorithm [59]. Here, we use a slightly modified defect correction procedure as described in section 3.2 and improve performance by implementing the optimisations discussed in our initial publication. The performance numbers are directly comparable as we continue to use the same test problem, namely the Poisson problem on the unit square with uniform refinement, cf. section 5.1. Furthermore, we add the emulated double-single floating point format and a multigrid solver with Jacobi smoothing to our GPU framework.

### 6.1 GPU-CPU configuration

For the solution of a linear equation system with an iterative refinement technique, the GPU executes the low precision (single float) inner solver (cf. section 3.2) as a co-processor to the general purpose CPU which accumulates the corrections and computes new defects in high precision (double float). For optimal performance of the inner solver the involved matrices and vectors must be stored locally and thus duplicated into the video memory of the graphics card. During this transfer, the conversion from double to single float is performed. The computed single precision correction is transferred back to main memory and later implicitly converted to double precision by the CPU in the

process of accumulating it to the current double precision solution vector.

Analogously, the computation is performed on the GPU alone when using the emulated double-single floating point format without any transfers of intermediate results. Again, the data is stored locally and the double precision values are split into their high- and low-order components during the transfer of the initial matrix and data. After the solution on the GPU, the two components of the result vector are read back and combined on the CPU in double precision to form the final high precision result.

The multigrid solver employs F-cycles and we configure it to perform 2+2 and 4+4 pre- and postsmoothing steps respectively. In our tests, we compare execution time (including all required transfers and setup times of the coprocessor) and accuracy of the solution against a carefully optimised version of the corresponding solver, taken from the FEAST package (cf. section 8.1).

We execute all performance tests on a high-end workstation PC with the following hardware details:

- CPU: AMD Athlon64 X2 4400+, 2.2 GHz, 2MB cache

- GPU: NVIDIA GeForce 7800 GTX, 24 fragment pipelines, 430 MHz, connected via PCIe x16 to an NFORCE4 chipset

- CPU memory: 2 GB DDR400, PC3200

- GPU memory: 256 MB DDR3, 600 MHz, memory interface 256 bit

Note that all tests are performed as single-threaded, serial jobs, and only benefit from the dual-core architecture in that other threads on the machine do not interfere with the computation.

We have also performed all tests on a comparable system with two Intel Xeon EM64T 3.6 GHz processors and a NVIDIA Quadro FX 4500 graphics card, and achieved similar results. We conclude that no high-end graphics card is required (the Quadro boards cost about four times as much as the mainstream GeForce models) for good performance, though this might be an issue in a cluster environment where reliability is of much higher importance than in a single workstation.

In the following paragraphs, we compare absolute performance of a double-single solver and the iterative refinement scheme as speedup against the CPU which computes in double precision. We also analyse relative performance and report on the actual iterations required until solution. All solvers are iterated until the norms of the residuals have been reduced by ten digits, and the iterative refinement schemes perform the high precision update step every two digits.

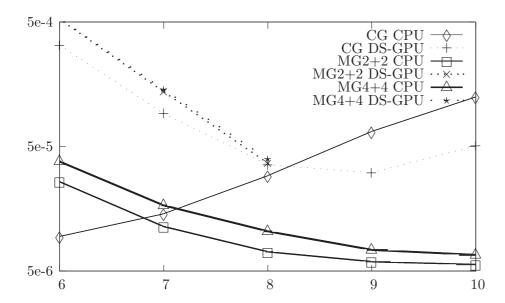

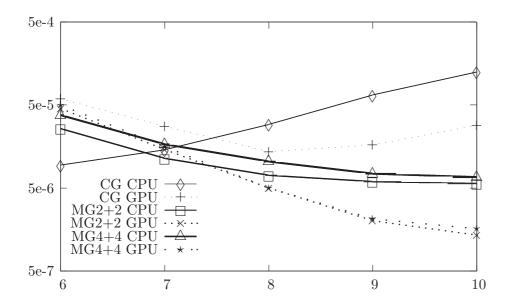

Figure 1. Normalised time until solution for the emulated double-single format (DS) with three different solvers (CG and MG with different number of smoothing steps) on the CPU and the GPU, for levels 6–10 (cf. section 6.3).

### 6.2 Emulation vs. CPU: Accuracy

We first confirm that the conjugate gradient solver delivers exactly the same accuracy as the CPU reference solver. Each level of refinement translates to the expected error reduction by a factor of four. The multigrid solver, however, cannot deliver the required precision and stalls for higher levels. Recall that during the multigrid cycles, the coarse grid correction term is computed, prolongated and then accumulated to the defect on finer levels. A detailed analysis of our implementation and the test problem reveals that at some point during the multigrid cycles (when the norm of the defect has dropped below 1e-12 (absolute values) already), very small corrections are added to a comparatively large (with respect to absolute values) intermediate approximation of the solution. The emulated floating point format is not able to capture these large differences properly, and the solution process stalls. We refer to the appendix for tables A1, A2 and A3 with the exact numbers.

## 6.3 Emulation vs. CPU: Performance

Figure 1 shows the absolute performance of the three solvers implemented in double precision on the CPU and the emulated double-single format on the GPU. The values are normalised to show the time until solution per unknown.