## Diplomarbeit

Entwurf einer Softwarebibliothek zur

Entwicklung portabler,

hardwareorientierter HPC Anwendungen

am Beispiel von Strömungssimulationen

mit der Lattice Boltzmann Methode

Dirk Ribbrock

4. August 2009

Gutachter:

Prof. Dr. Heinrich Müller Prof. Dr. Stefan Turek

Fakultät für Informatik Graphische Systeme (LS VII) Technische Universität Dortmund http://ls7-www.cs.tu-dortmund.de Fakultät für Mathematik Angewandte Mathematik und Numerik (LS III) Technische Universität Dortmund http://www.mathematik.tu-dortmund.de/lsiii/

# Inhaltsverzeichnis

| 1 | Einl                 | Einleitung 1                                           |    |  |  |  |

|---|----------------------|--------------------------------------------------------|----|--|--|--|

|   | 1.1                  | Motivation                                             | 1  |  |  |  |

|   | 1.2                  | HONEI LBM                                              | 2  |  |  |  |

|   | 1.3                  | Überblick                                              | 3  |  |  |  |

|   | 1.4                  | Verwandte Arbeiten                                     | 4  |  |  |  |

| 2 | HPO                  | C Hardware                                             | 7  |  |  |  |

|   | 2.1                  | CPU                                                    | 7  |  |  |  |

|   |                      | 2.1.1 Multicore                                        | 8  |  |  |  |

|   |                      | 2.1.2 Cluster                                          | 10 |  |  |  |

|   | 2.2                  | GPU                                                    | 10 |  |  |  |

|   | 2.3                  | Cell BE                                                | 14 |  |  |  |

| 3 | Dia                  | Lattice Boltzmann Methode für die Flachwassergleichung | 19 |  |  |  |

| 3 | Die                  | Lattice Boitzmann Wethode for the Flachwassergielchung | 19 |  |  |  |

| 4 | HONEI                |                                                        |    |  |  |  |

|   | 4.1                  | $\ddot{\mathrm{U}}\mathrm{bersicht}$                   | 25 |  |  |  |

|   | 4.2                  | HONEI Komponenten                                      | 26 |  |  |  |

|   |                      | 4.2.1 Util                                             | 27 |  |  |  |

|   |                      | 4.2.2 Hardware Backends                                | 29 |  |  |  |

|   |                      | 4.2.3 Unittest                                         | 32 |  |  |  |

|   |                      | 4.2.4 Benchmark                                        | 32 |  |  |  |

|   |                      | 4.2.5 LA                                               | 32 |  |  |  |

|   |                      | 4.2.6 Math                                             | 34 |  |  |  |

|   |                      | 4.2.7 LBM                                              | 34 |  |  |  |

|   |                      | 4.2.8 SWE                                              | 34 |  |  |  |

|   | 4.3 Neuentwicklungen |                                                        |    |  |  |  |

|   |                      | 4.3.1 Memory Arbiter                                   | 34 |  |  |  |

|   |                      | 4.3.2 CUDA Backend                                     | 36 |  |  |  |

|   |                      | 4.3.3 MPI Backend                                      | 38 |  |  |  |

|   |                      | 4.3.4 SolverLABSWE                                     | 39 |  |  |  |

|   |                      | 4.3.5 Visualisierung                                   | 40 |  |  |  |

## Inhaltsverzeichnis

| 5                    | HO   | NEI LB     | SM Grid                       | 43   |  |  |  |  |  |

|----------------------|------|------------|-------------------------------|------|--|--|--|--|--|

|                      | 5.1  | Daten      | strukturen                    | . 43 |  |  |  |  |  |

|                      |      | 5.1.1      | Grid                          | . 43 |  |  |  |  |  |

|                      |      | 5.1.2      | PackedGridData                | . 44 |  |  |  |  |  |

|                      |      | 5.1.3      | PackedGridInfo                | . 45 |  |  |  |  |  |

|                      |      | 5.1.4      | PackedGridFringe              | . 46 |  |  |  |  |  |

|                      | 5.2  | Solver     | LBMGrid                       | . 47 |  |  |  |  |  |

|                      |      | 5.2.1      | Die do_preprocessing Methode  | . 48 |  |  |  |  |  |

|                      |      | 5.2.2      | Die do_postprocessing Methode | . 48 |  |  |  |  |  |

|                      |      | 5.2.3      | Die solve Methode             | . 48 |  |  |  |  |  |

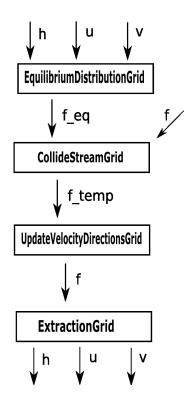

|                      |      | 5.2.4      | EquilibriumDistributionGrid   | . 50 |  |  |  |  |  |

|                      |      | 5.2.5      | CollideStreamGrid             | . 53 |  |  |  |  |  |

|                      |      | 5.2.6      | UpdateVelocityDirectionsGrid  | . 54 |  |  |  |  |  |

|                      |      | 5.2.7      | ExtractionGrid                | . 55 |  |  |  |  |  |

| 6                    | Erge | Ergebnisse |                               |      |  |  |  |  |  |

|                      | 6.1  | Verwe      | ndete Hardware                | . 57 |  |  |  |  |  |

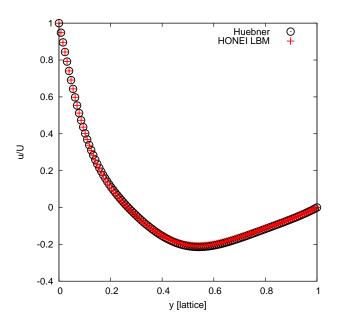

|                      | 6.2  | Korre      | ktheit                        | . 59 |  |  |  |  |  |

|                      | 6.3  | Bench      | marks                         | . 62 |  |  |  |  |  |

|                      |      | 6.3.1      | Kernelbenchmarks              | . 62 |  |  |  |  |  |

|                      |      | 6.3.2      | Löserbenchmarks               | . 66 |  |  |  |  |  |

|                      |      | 6.3.3      | Cluster und Skalierbarkeit    | . 70 |  |  |  |  |  |

| 7                    | Zus  | ammen      | fassung                       | 75   |  |  |  |  |  |

| Literaturverzeichnis |      |            |                               |      |  |  |  |  |  |

# 1 Einleitung

## 1.1 Motivation

In den letzten Jahren zeichnet sich ab, dass die Rechenleistung der einzelnen klassischen CPU nicht mehr stark ansteigt, da sie sehr stark durch Wärmeverlustleistung und andere physikalische und elektrotechnische Grenzen eingeschränkt wird. Gleichzeitig hinkt die Geschwindigkeit des Arbeitsspeichers und seiner Anbindung an die CPU dem Bedarf wissenschaftlicher Rechnens weit hinterher. Ein typisches System, dass eine Fließkommaleistung in einfacher Genauigkeit von 96 GFlop/s <sup>1</sup>, aber nur eine Speichertransferrate von 12 GByte/s (das entpricht  $3 \cdot 10^9$  Fließkommazahlen in einfacher Genauigkeit pro Sekunden) besitzt, müsste also mit jeder transferierten Fließkommazahl mindestens 32 Berechnungen durchführen, um die theoretische Maximalleistung (peak performance) zu erreichen. Dies lässt noch außer Acht, dass das Ergebnis der meisten Berechnungen auch noch in den Arbeitsspeicher zurückgeschrieben werden muß. Um für eine Operation einschätzen zu können, wie stark sie durch dieses Missverhältnis zwischen Rechen- und Speichergeschwindigkeit beeinflusst wird, eignet sich die arithmetische Intensität, die das Verhältnis von durchgeführten Fließkommaoperationen zu notwendigen Speichertransfers angibt. Im obigen Beispiel entspricht die arithmetische Intensität  $\frac{N_{\text{flop}}}{N_{\text{transfer}}} = \frac{96}{3} = 32$ . In der Praxis sind allerdings arithmetische Intensitäten von 1 oder weniger sehr verbreitet. So hat etwa die komponentenweise Summe von zwei Vektoren eine arithmetische Intensität von  $\frac{N_{\mathrm{flop}}}{N_{\mathrm{transfer}}} = \frac{1}{3} = 0,33$ . Hier ist es nämlich notwendig jeweils beide Operanden zu laden, die Addition durchzuführen und danach das Ergebnis wieder zu speichern. Ihre Ausführungsgeschwindigkeit ist also sehr stark durch die Speichertransferrate und weniger durch die eigentliche Geschwindigkeit der CPU beschränkt. Dieses Problem wird auch als memory wall [56] bezeichnet.

Inzwischen gibt es verschiedene Entwicklungen um diesem Problem zu begegnen. So wird bei Multicore CPUs nicht nur die Anzahl der Rechenkerne sondern auch die Anzahl der Speichercontroller erhöht. Gleichzeitig gibt es komplette Neuentwicklungen wie die Cell BE, bei der schon während des Entwurfs auf eine gute Speicheranbindung geachtet wurde. Außerdem sind Grafikkarten, die ursprünglich nur zur Beschleunigung und Berechnung von Computergrafik entworfen wurden, inzwischen in der Lage, auch Berechnungen auszuführen, die früher der CPU vorbehalten waren. Zuletzt verspricht das Vernetzen von

$<sup>^{-1}1 \</sup>text{ GFlop/s} = 10^9 \text{ Flop/s}$  (Floating point operations per second)

#### 1 Einleitung

sehr vielen herkömmlichen Rechnern zu einem Cluster eine deutliche Erhöhung der Ausführungsgeschwindigkeit bei sehr großen Problemstellungen, da die theoretische Rechenkapazität deutlich erhöht wird.

Um diese heutige Hardware optimal auszunutzen, muss man bei der Entwicklung von Applikationen auf die speziellen Eigenschaften der Hardware eingehen. Moderne Architekturen wie Cell BE, GPU oder ganze Computercluster haben auf den ersten Blick nicht viele Gemeinsamkeiten. Da man eine Applikation aber nicht für jede Hardware komplett neu schreiben will, wird versucht, durch Basisbibliotheken von der Hardware zu abstrahieren. Allerdings kann üblicherweise die Rechenkapazität jeder Hardware nicht voll ausgenutzt werden, indem man eine neue Applikation auf einer Reihe von gegebenen hardwareoptimierten Basisoperationen aufsetzt (z.B. BLAS [19]). Dieser zunächst naheliegende Ansatz erlaubt es oftmals nicht, die Möglichkeiten der jeweiligen Hardware in Verbindung mit den Eigenarten der speziellen Anwendung voll auszunutzen.

## 1.2 HONEI LBM

Die in dieser Arbeit vorgestellte Softwarebibliothek namens HONEI [11] versucht eine Lösung für diese Problemstellung zu finden, indem ein Kompromiss zwischen Portabilität und Hardwarenähe erreicht wird.

Die Tauglichkeit von HONEI soll am Beispiel von Strömungssimulationen (Computational Fluid Dynamics, CFD) mit der Lattice Boltzmann Methode (LBM) [60] evaluiert werden. Dabei wird die ein vereinfachtes Stömungsmodell, die sogenannten Flachwassergleichungen, verwendet. Hierbei werden nur solche Strömungen betrachtet, bei denen vertikale Effekte bei der Berechnung der Fluidbewegung vernachlässigt werden können, also die Wellenlänge wesentlich größer als die Wellenhöhe ist. Diese Methode erscheint insbesondere deshalb geeignet, da sie sehr lokal auf ihren Daten arbeitet, ein hohes Parallelisierungspotential besitzt und als rechenintensiv gilt, das heißt eine hohe arithmetische Intensität besitzt. Demgegenüber steht der relativ hohe Speicherverbrauch der Lattice Boltzmann Methode, da zur Berechnung eines jeden Elements der Wasseroberfläche sehr viele Geschwindigkeits- und Verteilungsfunktionen gespeichert werden müssen.

Obwohl die verwendeten Flachwassergleichungen durch die genannten Anforderungen scheinbar nur auf wenige Szenarios beschränkt sind, besitzen sie in der Praxis eine Vielzahl von verschiedenen Anwendungen. Insbesondere lassen sich damit nicht nur Wasserströmungen berechnen, sondern alle Phänomene, die ein inkompressibles Fluid beschreiben. Mögliche Anwendungen sind die Vorhersage von Tsunamis oder Sturmfluten und die Simulation von atmosphärischen Strömungen nicht nur auf der Erde sondern auch auf anderen Himmelskörpern. Daneben gibt es viele weitere Anwendungen im Bereich der CFD, wie das Um- bzw. Durchströmen von Fahrzeugen und Geräteteilen bis hin zu Anwendungen in der Unterhaltungsindustrie und sogar der Simulation des Blutflusses etwa durch eine

künstliche Herzklappe. Ausserhalb der CFD kann die LBM zum Beispiel auch zu Simulationen im Bereich der Quantenmechanik [46] verwandt werden. Dazu muss natürlich die in dieser Arbeit verwendete Flachwassergleichung durch eine andere ersetzt werden. Die wesentlichen hier erarbeiteten Eigenschaften und Konzepte behalten aber ihre Gültigkeit.

Schon 1950 berechneten John von Neumann et al. [8] auf dem ENIAC, einem der ersten damaligen Großrechner, eine Wettervorhersage für 24 Stunden. Dazu wurde ein 15×18 Gitter mit einer quadratischen Zellengröße von 736 km und Zeitschritte im Bereich von ein bis drei Stunden verwendet. Die eigentliche Berechnung dauerte mehrere Stunden und konnte im Anschluß mit der tatsächlichen Wetterentwicklung verglichen werden. Die Ergebnisse wichen zwar noch weit von einander ab, zeichneten aber die Richtung der rechnergestützten Wettervorhersage vor. Damals wie heute beschränkt die verfügbare Rechenleistung die erzielbare Genauigkeit der Ergebnisse im wissenschaftlichen Hochleistungsrechnen (high performance computing, HPC).

Im Rahmen dieser Arbeit wurde aufbauend auf den Ergebnissen der Projektgruppe SmartCell [42] an der TU Dortmund die Softwarebibliothek HONEI stark erweitert. Insbesondere die Komponenten Util und LA, sowie die hardwarenahen Bibliotheken für SSE und Multicore wurden wesentlich überarbeitet, erweitert oder komplett neugeschrieben. Dies wurde notwendig um softwaretechnische Einschränkungen, die sich während der ursprünglichen Entwicklung gezeigt hatten, zu beheben. Gleichzeitig war es nur durch wesentliche Veränderungen möglich, insbesondere die neu entwickelte Speicherverwaltung mit den restlichen Komponenten zu verbinden, da diese im ursprünglichen Entwurf der Projektgruppe nicht vorgesehen war. Die gesamte Multicore Unterstützung hatte sich bereits im Laufe der Projektgruppe als nicht performant erwiesen und musste deshalb neu konzipiert werden.

Zusätzlich wurden HONEI folgende neue Komponenten hinzugefügt:

- eine Speicherverwaltung, insbesondere für Systeme mit getrennten Speichern, wie es etwa zwischen Hauptspeicher und Grafikkartenspeicher der Fall ist

- hardwarenahe Bibliotheken für Cluster und Grafikkarten

- zwei eigenständige Lattice Boltzmann Löser

- eine Applikation zur Visualisierung der durch die Lattice Boltzmann Löser berechneten Strömungssimulationen

## 1.3 Überblick

Kapitel 1 enthält diese Einleitung und eine Zusammenfassung ähnlicher Veröffentlichungen. Kapitel 2 gibt einen Überblick über die in dieser Arbeit betrachteten Hardwarearchitekturen. Aufbauend auf der gewöhnlichen CPU werden SSE, Multicore und Cluster vorgestellt. Außerdem werden Architekturen wie Grafikkarten und die Cell BE erläutert, die zunächst

## 1 Einleitung

garnicht für diese Art von Berechnungen entwickelt wurden. Kapitel 3 stellt die Lattice Boltzmann Methode vor, die die Grundlage der in dieser Arbeit entwickelten Löser darstellt. Kapitel 4 beschreibt die HONEI Bibliothek und geht im zweiten Teil besonders auf die in dieser Arbeit neu entworfenen Komponenten ein. Kapitel 5 schließlich stellt den eigentlichen optimierten Lattice Boltzmann Löser vor, der darauf in Kapitel 6 ausführlich auf vielen Architekturen untersucht wird. Kapitel 7 fasst zuletzt die erarbeiteten Ergebnisse und gewonnenen Erkenntnisse zusammen und erörtert offene Fragestellungen.

## 1.4 Verwandte Arbeiten

Es existieren viele Arbeiten zur Beschleunigung der LBM auf verschiedenen Architekturen. Die Leistung aktueller Prozessoren von Intel, AMD und IBM mit Blick auf die LBM untersuchen Wellein et al. [54]. Sie vergleichen diese mit alten und neuen dedizierten HPC-Architekturen.

Einen Schritt weiter gehen Zeiser et al. [57] indem sie einen LBM Löser als Benchmarksystem für eben diese Prozessoren einsetzen und über die Leistung des LBM Lösers auf die generelle Leistungsfähigkeit für HPC Anwendungen schließen.

Die Optimierung eines LBM Lösers auf einen x86-64 Prozessor beschreibt im Detail Hausmann [23]. Er stellt insbesondere die besondere Bedeutung von vektorisierten Operationen auch für gewöhnliche x86 Prozessoren heraus, um hohe Leistungen zu erreichen.

Wilke et al. [55] behandeln dem gegenüber insbesondere die Optimierung eines LBM Lösers auf die Speicherhierachie aktueller Prozessorsysteme.

Speziell Multicore Architekturen werden durch Donath [10] untersucht. Hierbei kommt zur Optimierung der Kommunikation ein raumteilender Baum zum Einsatz, wie er normalerweise in der Computergrafik zum schnellen Ausschluss nicht zu rendernder Objekte genutzt wird.

Die Eignung der LBM für stark parallele Großrechner untersuchen Pohl et al. [44] und Wellein et al. [53]. Erstere untersuchen neben der Skalierbarkeit auch die wirtschaftlichen und umwelttechnischen Kosten der einzelnen Architekturen in Hinblick auf die Leistungsfähigkeit der verwendeten LBM Löser. Letztere versuchen einen möglichst kompletten Überblick über alle zur Zeit aktuellen Großrechner zu geben und deren jeweilige Eignung für die LBM einzuschätzen.

Die direkte Berechnung der LBM durch Grafikkarten mittels der eigentlich zur Grafikberechnung vorgesehenen Programmierschnittstellen beschreiben Li et al. [34]. In erster Linie wird hier die generelle Vorgehensweise beschrieben, um Berechnungen, die nicht der Grafikkarstellung dienen, auf einer Grafikkarte durchzuführen. Es werden eine Reihe von Techniken vorgestellt, um auf Basis von Pixel- und Texturoperationen Berechnungen durchzuführen, die zur Lösung der LBM notwendig sind und die notwendigen Datenstrukturen als Texturen zu repräsentieren.

Speziell die Implementierung eines CUDA LBM Lösers behandeln Tölke [52] und Zhao [59]. Hierbei simmuliert Tölke den Fluss durch ein poröses Medium, während Zhao hauptsächlich die LBM zur Bildbearbeitung nutzt. Beide Autoren stellen das CUDA Programmiermodell zur Programmierung der Grafikkarte mit einer sehr großen Anzahl von Threads vor.

Stürmer et al. [50] untersuchen die Simulation von Blutfluss auf der Cell BE um es Medizinern zu ermögliche, die Bildung von Anheurismen besser zu verstehen.

Die Parallelisierung der LBM zur Ausführung auf einem Cluster beschreiben Körner et al. [33]. Hierbei wird insbesondere die lokalität in Zeit und Raum der LBM herausgearbeitet und eine ausführliche Anleitung zur Parallelisierung derselben gegeben.

Speziell die Parallelisierung mit Hilfe von MPI erläutern Thürey et al. [51]. Sie gehen dabei besonders auf die adaptive Zerlegung des Rechengebiets ein um die Rechenlast optimal auf verschiedene Rechner im Cluster verteilen zu können.

Als erste haben Fan et al. [12] die Eignung eins GPU Clusters für wissenschaftliche Berechnungen untersucht und zur Evaluierung einen LBM Löser herangezogen.

Allen vorherigen Arbeiten gemein ist, dass sie ihre Untersuchungen auf eine spezifischen Zielarchitektur ausgerichtet haben. Ein LBM Löser, der ähnlich dem in dieser Arbeit vorgestellten, ganz verschiedene Hardwarearchitekturen unterstützt, wird von Peng et al. [40] vorgestellt und analysiert. Um einen hohen Grad an Parallelität zu erreichen, werden hier jeweils zwei Versionen der eigentlichen Datenstrukturen verwendet und damit der Speicherverbrauch verdoppelt. In die eine Version werden jeweils die aktuellen Ergebnisse geschrieben, während diese aus der anderen, die die Ergebnisse des vorherigen Zeitschritts bereitstellt, gelesen werden. Nach jedem Zeitschritt werden die Rollen vertauscht.

Die Erkenntnisse aus der Arbeit von Mallach [36] bezüglich des Entwurfs eines Multicore Backends, das auch bei geringen Problemgrößen die Berechnung nicht durch einen hohen Verwaltungsaufwand ausbremst, flossen in die Entwicklung des hier gezeigten Multicore Backends ein.

Parallel zu dieser Arbeit erweitert Geveler [16] den in Kapitel 5 vorgestellten LBM Löser um die Möglichkeit mit Bodenprofilen und Festkörpern zu interagieren.

1 Einleitung

## 2 HPC Hardware

Im Folgenden werden die unterschiedlichen Hardwarearchitekturen, die im Rahmen dieser Arbeit betrachtet wurden. Im Rahmen des wissenschalftlichen Rechnens geht es dabei insbesondere um ihre Eignung für Fließkommaoperationen.

## 2.1 CPU

Der althergebrachte Weg, um die Rechenleistung einer CPU zu beschleunigen war die Erhöhung ihrer Taktfrequenz. Mit Taktfrequenzen um vier GHz stießen die Hersteller aber zunehmend an elektrotechnische und physikalische Grenzen, insbesondere weil sich die Wärmeverlustleistung und damit auch die Energieeffizienz in nicht mehr vertretbare Dimensionen entwickelte [43] und die Signallaufzeit an sich nicht mehr erhöht werden konnte. Analog zu der schon angesprochenen memory wall, wird dieses Phänomen als power wall bezeichnet. Gleichzeitig erscheint es nicht mehr weiter möglich, durch gleichzeitiges Abarbeiten mehrerer im Programmquelltext aufeinander folgender Befehle einen weiteren Geschwindigkeitsgewinn zu erreichen. Viele Befehle beeinflussen den nachfolgenden Programmfluss und dadurch sind der Parallelität auf Instruktionsebene (instruction-level parallelism) sehr häufig Grenzen gesetzt. Diese Grenze wird als ILP wall bezeichnet.

Im Folgenden sollen verschiedene Techniken vorgestellt werden, wie trotz der genannten Grenzen die Rechenleistung einer CPU weiter erhöht werden kann.

FPU Sehr alte x86 Prozessoren (bis einschließlich Intel 80486) mussten Fließkommaberechnungen in Software auf den Fixpunktrecheneinheiten simulieren, da sie keine Recheneinheit für Fließkommazahlen, die sogenannte Floating Point Unit (FPU), besaßen. Da dies sehr langsam war, gab es die Möglichkeit eine FPU als externen Koprozessor nachzurüsten, um die CPU zu entlasten. Die FPU arbeitet auch heute noch mit einem Stackspeicher und kann deshalb nur eine Fließkommaoperation gleichzeitig ausführen. Ab dem Intel Pentium Prozessor ist diese FPU auf Grund sinkender Kosten in der Produktion von Prozessoren fest in die CPU integriert.

MMX Um die Anzahl der möglichen Rechenoperationen pro Sekunde neben den normalen Fortschritten durch einen beschleunigten Prozessortakt weiter zu erhöhen, wurde zunächst von Intel die MMX-Technologie entwickelt und erstmals im Intel Pentium Prozessor ver-

baut. Hierbei werden die schon vorhandenen 80 Bit Register des Stackspeichers der FPU auf acht 64 Bit Integerregister abgebildet, auf die wahlfrei zugegriffen werden kann. Diese Vektorregister können einen 64 Bit Integer oder zwei 32 Bit Integer oder vier 16 Bit Integer speichern. Damit wird es möglich, auf allen in einem Register gespeicherten Daten ein und dieselbe Rechenoperation durchzuführen. Durch Anwendung dieses sogenannten Single Instruction Multiple Data (SIMD) Prinzips [14] vervierfacht sich in diesem Fall die Anzahl der pro Sekunde ausgeführten Rechenoperationen. Zum Beispiel können die in den Registern A und B gespeicherten Zahlen  $A = (a_3, a_2, a_1, a_0)$  und  $B = (b_3, b_2, b_1, b_0)$  durch die SIMD Operation C = A + B gleichzeitig elementweise addiert und in dem Register  $C = (c_3, c_2, c_1, c_0)$  gespeichert werden:

$$c_0 = a_0 + b_0$$

$c_1 = a_1 + b_1$

$c_2 = a_2 + b_2$

$c_3 = a_3 + b_3$

Diese Technik wird schon seit langem in Großrechnern, genauer Vektorrechnern [27] verwendet. Da die MMX und FPU Register physikalisch identisch sind, ergeben sich allerdings Probleme, da nur entweder MMX oder FPU genutzt werden können. Gleichzeitig können mit MMX keine Fließkommaoperationen sondern nur Integeroperationen ausgeführt werden.

SSE Diese Einschränkungen führten zu der Entwicklung von SSE (Streaming SIMD Extensions) [28], die erstmals im Intel Pentium II verwendet wurden und acht neue physikalische 128 Bit Register in der CPU hinzufügten. Prozessoren, die die x86-64 Erweiterung (AMD64 ab Athlon 64 / Intel64 ab Pentium 4) beinhalten, besitzen insgesamt sechzehn 128 Bit SSE Register. Diese SSE Register können jeweils vier 32 Bit Fließkommazahlen in einfacher Genauigkeit oder zwei 64 Bit Fließkommazahlen in doppelter Genauigkeit speichern. Die nachfolgenden Revisionen SSE2, SSE3 und SSE4, sowie ähnliche Initiativen von AMD (3DNow!, SSE4a) haben sowohl eine Unterstützung von SSE für Fixkommaoperationen eingeführt, als auch den Befehlsumfang über arithmetische Operationen auf Anwendungen der graphischen Datenverarbeitung und Multimedia erweitert. Außerdem werden nach und nach anfängliche Restriktionen, wie die Form der Speicheradressen, von denen Daten zwischen Hauptspeicher und SSE Register transferiert werden können, reduziert.

## 2.1.1 Multicore

Ein anderer Ansatz die Anzahl der gleichzeitigen Berechnungen zu steigern, ist die Anzahl der gleichzeitig ausgeführten Operationen auf unterschiedlichen Daten zu erhöhen. Dieses Prinzip wird Multiple Instruction, Multiple Data (MIMD) [14] genannt. Dies bedeutet auf

Seite der Software üblicherweise, dass das Programm in mehrere parallelen Handlungsstränge, sogenannte *Threads*, aufgeteilt wird. Diese Threads sollen nun von der CPU möglichst gleichzeitig ausgeführt werden.

Hyper-Threading Um den Aufwand an zusätzlichen Prozessorkomponenten möglichst gering zu halten, kann man sich zunächst darauf beschränken, nur die Registersätze zu duplizieren. Somit kann eine physikalische CPU als zwei logische CPUs vom Betriebssystem benutzt werden, da der Prozessor die Ausführung zwischen zwei Threads hin- und herschalten kann. Der Status des Threads bleibt währenddessen in seinen eigenen Registern gespeichert. Dies lohnt sich, da ein Thread sehr häufig auf andere Hardwarekomponenten warten muss, wie etwa den Arbeitsspeicher oder die Festplatte, und zu dieser Zeit selbst gar nicht die Recheneinheiten der CPU in Anspruch nimmt.

Multicore Echte Mehrkernprozessoren besitzen nun mehrere vollständig unabhängige Recheneinheiten (Multicore), also Kerne (Cores) mit eigenen Rechenwerken, Caches und teilweise auch Speichercontrollern. Theoretisch besitzt ein Zweikernprozessor die doppelte Rechenleistung seines einkernigen Gegenstücks. Einen Schritt weiter gehen Multiprozessorsysteme, die mehrere Mehrkernprozessoren auf einer Hauptplatine vereinen.

Betrachtet man die Mehrkernprozessoren der Hersteller Intel und AMD, so lassen sich insbesondere bei der Speicherhierachie wesentliche Unterschiede erkennen.

Bei den Prozessoren der Pentium D und Intel Core2 Familie besitzt jeder Kern einen eigenen L1-Cache aber alle Kerne teilen sich einen gemeinsamen L2-Cache. Der Zugriff auf den Hauptspeicher geschieht uniform über einen gemeinsamen Frontsidebus, der die Verbindung zum Speichercontroller auf der Hauptplatine herstellt. Im Gegensatz dazu besitzen Prozessoren der Intel Core i7 Familie und Prozessoren der AMD K9 Familie eigene L1- und L2-Caches pro Kern. Alle Kerne teilen sich lediglich einen L3-Cache. Gleichzeitig geschieht der Zugriff auf den Hauptspeicher nicht uniform über jeweils eigene Speichercontroller, die direkt im Chip integriert sind. Diese Art der Speicherarchitektur nennt man Non Uniform Memory Architecture (NUMA), da hier jeder Kern seinen eigenen Speicherbereich besitzt. Versucht ein anderer Kern auf diesen Bereich zuzugreifen, so geschieht dies über den erstgenannten Kern. Das bedeutet in der Regel, dass der Zugriff auf den eigenen Speicherbereich für einen Kern deutlich schneller ist, als auf die Speicherbereiche der anderen Kerne. Damit Daten, die ein Kern aus dem Speicherbereich eines anderen Kerns erhalten hat, nicht durch Schreib- oder Lesezugriffe anderer Kerne invalidiert werden, sorgt die CPU für sogenannte Cache-Kohärenz. Das bedeutet, dass sobald ein Kern ein Datum verändert, dies auch in den Caches aller anderen Kerne, die dasselbe Datum in ihrem eigenen Cache vorliegen haben, passiert. Dieses Verhalten, das auch als cache-coherent NUMA (ccNUMA) bezeichnet wird, vereinfacht die Programmierung dieser Systeme erheblich, da man immer davon ausgehen kann, dass der Zugriff auf eine Speicherstelle ein valides Ergebnis liefert. Die Core i7 und K9 Prozessoren gehören zu diesen ccNUMA Architekturen.

## 2.1.2 Cluster

Im Gegensatz zu den oben genannten NUMA Architekturen, bei denen die Synchronisation und Kommunikation auf einem Chip und über den L3-Cache realisiert ist, stellen die einzelnen Rechner (Knoten) eines Clusters [1] komplett eigenständige Computersysteme dar. Die Kommunikation zwischen den Knoten geschieht hier über die Netzwerkverbindung, durch die die einzelnen Knoten verbunden sind und ist damit deutlich langsamer als die Kommunikation innerhalb eines Multicorechips. So besitzt zum Beispiel der LiDO-Cluster [29] an der Universität Dortmund 224 einzelne Rechner (Knoten), die miteinander vernetzt sind. Zusammen besitzen die Knoten 1,216 TB Arbeitsspeicher. Dies ermöglicht das Bearbeiten von deutlich größeren Problemen, als es etwa mit einem einzelnen Computer möglich wäre, der heute üblicherweise maximal 8 bis 16 GByte Arbeitsspeicher besitzt. Gleichzeitig können bei derart großen Problemen tatsächlich alle eingesetzten Knoten die Gesamtrechenzeit verkürzen, ohne dass ein zusätzlich hinzugefügter Knoten mehr Verwaltungsaufwand erzeugt, als er die Rechenzeit verkürzt. Dieser Verwaltungsaufwand ist häufig notwendig, um die einzelnen rechnenden Knoten zu synchronisieren und zwischen ihnen die Rechenergebnisse der anderen Knoten zu kommunizieren.

Da in einem Cluster ein Knoten nicht direkt, wie es bei den Kernen einer Multicore-CPU in den bisher vorgestellen NUMA Architekturen der Fall war, auf Speicherbereiche eines anderen Knoten zugreifen kann, spricht man hier auch von einer Distributed Memory Architektur. Hier ist es notwendig, dass die Programme, die auf den Knoten ausgeführt werden, einen notwendigen Transfer von Daten aus dem Arbeitsspeicher eines Knoten in den Arbeitsspeicher eines anderen Knoten explizit anstoßen. Um dies zu vereinfachen, gibt es Kommunikationsstandards, wie das Message Passing Interface (MPI) [49] [21], das den Nachrichtenausstausch und damit die Kommunikation zwischen den Knoten eines Clusters beschreibt. Bei MPI geschieht die Kommunikation durch Nachrichten, die zwischen zwei oder mehr Knoten verschickt werden. Diese Nachricht enthalten dann zum Beispiel den Inhalt eines Speicherbereichs, den ein Knoten einem anderen zur Verfügung stellt, damit dieser die Daten bearbeitet und eventuell später wieder zurückschickt. Durch die Möglichkeit, den Programmfluß von Sender und Empfänger zu blockieren, können die einzelnen Knoten ihre Programmausführung synchronisieren, da alle beteiligten Knoten darauf warten, dass die Kommunikation abgeschlossen wird.

## 2.2 **GPU**

Überblick Grafikkarten [13] müssen in der Lage sein, eine sehr große Menge an Daten sehr schnell zu verarbeiten, um Grafiken in Echtzeit darstellen zu können. Die Art und

Weise wie diese Berechnungen durchgeführt werden, hat zu einer sehr fein parallelisierten Hardwarearchitektur geführt, bei der das Hauptaugenmerk auf einem maximalen Durchsatz und weniger auf der schnellen Berechnung eines einzelnen Pixelwertes liegt. Die hierdurch erreichte theoretische Fließkommmaleistung liegt bei aktuellen Grafikkarten, wie der NVIDIA GeForce GTX 285, bei etwa 1000 GFlop/s in einfacher Genauigkeit. Der Zugriff auf den Speicher der Grafikkarte erfolgt mit einer Transferrate von etwa 160 GByte/s.

Diese eigentlich aus dem Bedarf der Grafikverarbeitung entstandene Rechenleistung möchte man nun auch für andere Berechnungen nutzbar machen. Die Verwendung einer Grafikkarte um allgemeine Berechnungen durchzuführen, die gewöhnlich nur auf der CPU ausgeführt werden, wird als general-purpose computing on graphics processing units (GPGPU) [39] bezeichnet.

Da die Untersuchungen in dieser Arbeit auf aktuellen Grafikkarten von NVIDIA [35] durchgeführt wurden, soll im Folgenden die Architektur dieser Hardware genauer beschrieben werden.

Aufbau Wie weiter oben angeführt, besitzt eine Grafikkarte eine sehr stark parallelisierte Architektur. Um dies zu erreichn, folgt ihr Aufbau dem Schema, eine große Menge sehr kleiner Recheneinheiten zu immmer größeren Strukturen zusammenzufassen.

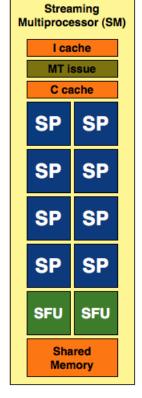

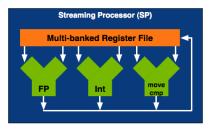

Das atomare Bauteil der GT 200 Serie, zu der auch die oben erwähnte GeForce GTX 285 gehört, ist der sogenannte Streaming Processor (SP) (Abbildung 2.1a), ein Mikroprozessor mit einer Einheit für Vergleiche und zur Berechnung von Sprungadressen, einer Integerund einer Fließkommarecheneinheit. Der SP besitzt keinen eigenen Cache und vermag nicht viel mehr als mathematische Operationen durchzuführen. Damit könnte man ihn als stark vereinfachte Version einer SPE, wie sie in Abschnitt 2.3 beschrieben wird, auffassen.

Fasst man nun mehrere dieser Streaming Prozessoren zusammen, so erhält man einen Streaming Multiprocessor (SM) (Abbildung 2.1b). Ein SM besteht aus acht SPs und zwei weiteren sogenannten Special Function Units (SFU), die für trigonometrische Funktionen und Interpolationen zuständig sind. Alle diese Recheneinheiten erhalten ihre Aufgaben von einer übergeordneten Einheit mit Namen Multithreaded instruction fetch and issue unit (MT Issue), die die Operationen an die Prozessoren verteilt. Zu diesem Zwecke stehen ein kleiner Befehlscache (I cache), ein kleiner Cache für konstante Daten (C Cache) und ein zwischen allen Recheneinheiten gemeinsam geteilter 16 kByte großer Speicher (Shared Memory) zur Verfügung. Der SM ist in der Lage 1024 Threads parallel auszuführen. Gleichzeitig geschieht das Umschalten zwischen Threads komplett durch die Hardware, weshalb dies ohne Verzögerung möglich ist.

Die SMs werden jeweils zu dritt zu einem Texture Processor Cluster (TPC) (Abbildung 2.1c) zusammengefasst. Zusätzlich enthält ein TPC wiederum eine Steuereinheit (Streaming Multiprocessor Controller (SMC)) und einen gemeinsamen Texturspeicher (Texture L1).

(a) Streaming Processor

$\begin{array}{cc} \text{(b)} & \text{Streaming} & \text{Multiprocessor} \\ \end{array}$

(c) Texture Processor Cluster

Abbildung 2.1: Schemata der einzelne Grafikkartenkomponenten (Quelle: NVIDIA)

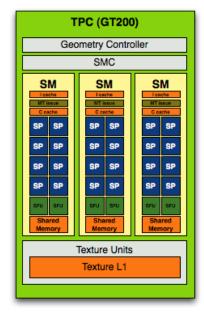

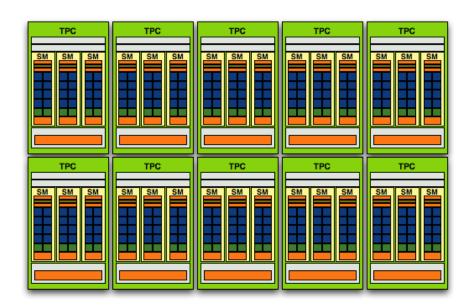

Abbildung 2.2: Schema eines Streaming Processor Array (Quelle: NVIDIA)

Schließlich sind zehn dieser TPC zu einem Streaming Processor Array (SPA) (Abbildung 2.2) kombiniert. Somit befinden sich auf der Grafikkarte insgesamt 30 MPs bzw. 240 SPs.

Demgegenüber steht eine Speicherhierachie, die auf oberster Ebene ein bis zwei Gbyte globalen Grafikkartenspeicher zur Verfügung stellt. Dieser kann entweder als normaler Arbeitsspeicher aufgefasst oder alternativ auch als Texturspeicher angesprochen werden. Im zweiten Fall kann nur lesend darauf zugegriffen werden. Diese Lesezugriffe werden aber in zwei Dimensionen gepuffert und unterstützen damit optimal die Arbeit mit Texturen und anderen in zwei Dimensionen lokalen Daten. Jeder Chip enthält zusätzlich 64 kByte sehr schnellen sogenannten "konstanten Speicher", auf den alle Threads zugreifen können. Auf die Threads eines SM beschränkt ist der Zugriff auf den schon angesprochenen 16 kByte großen Speicher, den jeder SM besitzt. Schließlich besitzt jeder SM 16384 Hardwareregister, in denen die Daten aller von ihr ausgeführten Threads gespeichert werden. Erscheint diese Zahl zunächst recht hoch, so ergibt sich bei einer vollen Auslastung eines SM mit 1024 Threads eine maximale Registeranzahl von 16 Registern pro Thread.

Ein auf der Grafikkarte ausgeführtes Programm besteht nun aus sehr vielen Threads, die alle dieselbe Folge von Operationen auf unterschiedlichen Daten ausführen. Bezugnehmend auf das oben angeführte SIMD Prinzip, nennt NVIDIA dies single instruction multiple thread (SIMT). Die einzelnen Threads werden in Blöcken organisiert. Viele dieser Blöcke bilden wiederum ein sogenanntes Gitter (Grid). Hierbei werden alle Threads eines Blocks auf einem einzelnen SM ausgeführt, können sich also über den geteilten Speicher der SM synchronisieren. Diese Threads sind in sogenannten Warps 1 zu je 32 Threads gegliedert. Alle Threads eines Warps laufen gleichzeitig auf ihrem SM und führen jeweils denselben Befehl aus. Es können sich allerdings mehrere Warps von Threads in einem Block bei der Ausführung auf einem SM abwechseln. Die ersten 16 und die letzten 16 Threads eines Warps können gemeinsam auf den Grafikkartenspeicher zugreifen und somit ihre Transfers zu einem einzigen gemeinsamen Speichertransfer (Coalescing) zusammenfassen. Dies kann die Speichertransferrate deutlich erhöhen, ist allerdings mit Einschränkungen verbunden. Damit alle 16 Transfers tatsächlich zu einem einzelnen Transfer verbunden werden können, müssen alle 16 in einem Warp benachbarten Threads auf 16 benachbarte Speicherstellen zugreifen. Dies bedeutet, dass wenn ein Thread i auf eine Speicherstelle jzugreift, der Thread i+1 nur auf die Speicherstelle j+1 zugreifen kann. Im Gegensatz zu Grafikkarten der GeForce 8 Serie, bei denen eine kleine Verletzung dieser Regel durch einen der 16 Threads bereits eine sehr starke Aufteilung der Speichertransfers bedeutete, kann der Speichercontroller der GT 200 Serie auch solche Speicherzugriffe zu möglichst wenigen Transfers zusammenfassen.

Jedes Mal wenn ein SM den nächsten Befehl ausführen kann, wird durch die MT Issue Einheit ein Warp von Threads ausgewählt, der gerade bereit ist und nicht auf ausstehende

<sup>&</sup>lt;sup>1</sup>(Eine Webkette (engl.: Warp) entspricht auf einem echten Webstuhl einer vertikalen Gruppe paralleler Fäden (engl.: Thread)

#### 2 HPC Hardware

Datentransfers wartet, da die Latenz beim Zugriff auf den Grafikkartenspeicher durchaus mehr als 1000 Takte betragen kann. An dieser Stelle wird wieder deutlich, dass das grundlegende Design der Grafikkarte auf reinen Durchsatz ausgelegt ist, da es nahezu keine Cache-Hierachie gibt, die etwaige Zugriffe auf den Grafikkartenspeicher beschleunigen würde, wie es ähnliche Cache-Hierachien bei der normalen CPU leisten. Im Optimalfall müssen alle Threads eines Warps denselben Befehl ausführen, sodass alle Threads dies gleichzeitig tun können. Weichen die auszuführenden Befehle der einzelnen Threads durch vorherige Verzweigungen im Programmfluss voneinander ab, so berechnet jeder Thread des Warps beide möglichen Programmpfade und verwirft am Ende das nicht gültige Ergebnis, bis alle Threads wieder denselben Zustand erreicht haben.

## 2.3 Cell BE

Überblick Die Cell-Broadband Engine wurde vom STI Design Center, einer Kooperation der Unternehmen Sony, Toshiba und IBM, entwickelt [30]. Sie wird zum Einen in der Spielekonsole Playstation 3 von Sony verbaut, ist zum Anderen aber auch direkt als Bladeserver erhältlich. So sind zum Beispiel im IBM Blade QS22 [32] zwei miteinander verbundene Cell Prozessoren eingebaut.

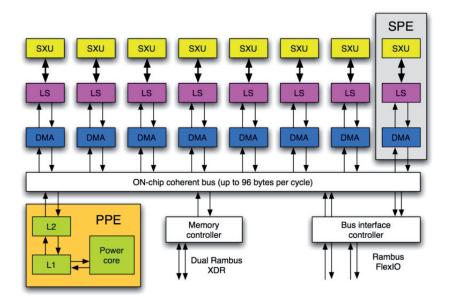

Im Gegensatz zu herkömmlichen Mehrkern-Prozessoren besteht der Cell-Prozessor nicht aus mehreren gleichartigen Kernen, sondern aus einer 64bit-PowerPC-CPU, dem sogenannten Power Processor Element (PPE), und bis zu acht sehr leistungsfähigen Vektorprozessoren, die als Synergistic Processing Elements (SPE) bezeichnet werden. Letztere sind nicht zu Steuerungsaufgaben, wie z.B. der Ausführung eines Betriebssystems fähig, aber insbesondere für Fließkommaberechnungen hocheffizient. Abbildung 2.3 zeigt den schematischen Aufbau des Cell-Prozessors.

Jede SPE verfügt im Cell-Prozessor nur über sehr wenig lokalen Speicher (genannt Local Store (LS)) und kann nicht direkt auf den Hauptspeicher zugreifen. Die Kommunikation zwischen dem Hauptspeicher und den lokalen Speichern der SPEs über einen gemeinsamen Speicherbus muss vom Programmierer explizit vorgegeben werden. Dies bedeutet einerseits einen sehr hohen Freiheitsgrad für den Programmierer, andererseits aber auch starke Einschränkungen auf Grund des verhältnismäßig kleinen direkt adressierbaren Speichers.

Durch die acht SPEs summiert sich die maximale (theoretische) Fließkommaleistung des Cell-Prozessors auf 230 GFlop/s bei einfacher Genauigkeit.

Die folgende tiefergehende Beschreibung der wesentlichen Komponenten des Cell-Prozessors nimmt Bezug auf die Darstellung von Kahle [30], in der auch weitere Details nachzulesen sind.

Das Power Processor Element Das Power Processor Element (kurz: PPE) verfügt über einen 32 kByte L1-Instruktions- und Daten-Cache, sowie eine Taktfrequenz von 3,2 GHz.

Abbildung 2.3: Schema des Cell-Prozessors (Quelle: Wikipedia)

2 Threads werden nach dem *Round-Robin Prinzip* zur gleichen Zeit verarbeitet (*dual-threaded*) und bis zu 2 Instruktionen können sich gleichzeitig in der Ausführungs-Phase befinden (*dual-issued*), solange sie nicht die gleiche Ausführungseinheit belegen.

Das Hauptmerkmal des Designs ist eine reduzierte Komplexität um eine hohe Taktrate und eine geringe Verlustleistung zu gewährleisten. So wurde zum Beispiel auf *Out-of-Order* Ausführung und eine komplexe Sprung-Vorhersage (*Branch-Prediction*) verzichtet.

Speichertransfers per DMA Wie alle Recheneinheiten des Cell-Prozessors verfügt das PPE über einen Speichercontroller namens Memory Flow Controller (MFC). Über ihn werden alle Transfers per DMA (Direct Memory Access) oder die im Verhältnis dazu langsameren MMIO (Memory-Mapped-I/O)-Register abgewickelt. Dabei ist es sowohl möglich, dass das PPE Daten zu den SPEs sendet, als auch, dass die SPEs ihrerseits mit ihren Memory Flow Controllern Daten vom Hauptspeicher des PPE anfordern. DMA-Speichertransfers sind grundsätzlich an 16-Byte Grenzen ausgerichtet und haben eine maximale Größe von 16 kByte. Sie dienen insbesondere der Übertragung von kontinuierlichen Datenbereichen aus dem Hauptspeicher in die lokalen Speicher der SPEs.

Sollen nicht kontinuierliche Bereiche übertragen werden, so bietet die Cell-Architektur das Konzept der Listentransfers. In diesem Fall werden bis zu 2048 DMA-Transfers mit jeweils 16 kByte Größe über ein vorgegebenes Schema zu einer DMA-Liste zusammengefasst. Alle Adressen einer DMA-Liste müssen dabei in den höherwertigen 32 Bit übereinstimmen. So sind theoretisch mit einer solchen Liste bis zu 32 MByte Übertragung möglich, was der 128-fachen Größe des Local Stores entspricht. SPEs können ihrerseits solche DMA-Listen

#### 2 HPC Hardware

im Local Store anlegen, typischerweise werden die Listen aber vom PPE (auf Grund der Kenntnis von Hauptspeicheradressen) vorbereitet. Anschließend werden sie entweder zur SPE übertragen, oder von der SPE vor dem eigentlichen DMA-Listentransfer per herkömmlichem DMA-Transfer geladen.

Eine andere Möglichkeit zur Kommunikation zwischen dem PPE und den SPEs ist das Mailbox-System, welches ebenfalls über den MFC und die MMIO-Register abgewickelt wird. Jede Recheneinheit besitzt gewissermaßen einen Maileingang und -ausgang. Mit diesem System ist es möglich, 32-bit Nachrichten auszutauschen, die auch unterbrechenden Charakter haben können (*Interrupt-Mails*).

Die Synergistic Processing Elements Die SPEs verfügen als SIMD Recheneinheiten über 128 Vektorregister mit 128 Bit und einen 256 kByte großen Local Store anstelle eines Caches. Die Ausführungs- und Zugriffszeiten sind dadurch vollständig vorhersagbar und nicht von Trefferraten im Cache abhängig. Die Anzahl der vorhandenen Register erlaubt eine hohe Ausnutzung der SIMD-Vektoreinheit für große Probleme. Dies ist vor allem für die Anwendungsoptimierung selbst interessant, während bei grundlegenden Operationen wie Additionen oder Multiplikationen eher wenige Register ausgenutzt werden können.

Die SPEs nutzen dual issue: Es können Berechnungen und verschiedene Speicheroperationen gleichzeitig durchgeführt werden. Ebenso wurde wie beim PPE auf In-Order-Execution gesetzt und Sprünge werden nicht durch die Hardware vorhergesagt. Mit Hilfe von branch hints kann der Programmierer oder Compiler hohe Kosten für branch misses verhindern. In so einem Fall werden 17 Instruktionen ab der Sprungadresse vorgehalten.

Da die SPEs in der Lage sindi, ein 3-Operanden-multiply add, also Multiplikation zweier Operanden inklusive Addition des Ergebnisses auf einen dritten Operanden, in einem Befehl auszuführen, können vektorisiert bis zu vier solche multiply-add-Instruktionen pro SPE gleichzeitig ausgeführt werden. Insgesamt handelt es sich dabei also um acht Operationen, wodurch bei 3,2 GHz theoretisch bis zu 25,6 GFlop/s erreicht werden. Aufsummiert für acht SPEs bedeutet dies eine maximale theoretische Leistung von 204,8 GFlop/s. Dieser Wert wurde bei Tests von IBM auch annähernd erreicht.

Der Local Store erfüllt ähnlich wie ein Cache die Aufgaben eines sehr schnellen Zwischenspeichers zwischen RAM und Prozessor. Er dient sowohl für den schnellen Zugriff auf per DMA-Transfer geholte Daten, wie auch als Ablageort für Zwischenergebnisse. Zum Ende einer typischen Berechnung werden die Ergebnisse dann erneut über DMA-Transfers in den Hauptspeicher des PPE zurückgeschrieben.

Wie bereits erwähnt besitzt jede SPE dazu einen eigenen Speicher-Controller, der die Zugriffe von außen auf den Local Store und umgekehrt steuert, also zum Beispiel Datenanfragen an den Hauptspeicher oder andere Local Stores.

Bus und Speicheranbindung des Cell Der sogenannte Element Interconnect Bus (kurz: EIB) verbindet die einzelnen Elemente des Cell Prozessors (PPE, 8 SPEs, E/A-Geräte) durch einen Ringbus miteinander. Es handelt sich dabei um 4 unidirektionale 16-Byte-Kanäle, die paarweise in entgegengesetzte Richtungen verlaufen. Die Daten werden pro Bustakt (halber Prozessor-Takt) einen Schritt weitergegeben, wodurch bis zu drei Übertragungen gleichzeitig je Kanal durchgeführt werden können. Somit sind bis zu 12 parallele Übertragungen und sehr hohe Datentransferraten möglich, was erforderlich ist, um die SPEs kontinuierlich mit Daten zu versorgen. Von IBM wurden über 200 GByte/s Datenrate bei 1,6 GHz Bustakt erreicht.

Auch die Anbindung an den Hauptspeicher muss genug Bandbreite bieten, um die neun Prozessoreinheiten mit Daten zu versorgen. Dafür sorgt das XIO Interface von Rambus, das im Dual-Channel-Betrieb Datenraten von bis zu 25,6 GByte/s erreicht. Die Kommunikation mit anderen Hardwarekomponenten geschieht über das FlexIO-Interface der Firma Rambus. Insgesamt sind bei 3,2 GHz Datenraten von 44,8 GByte/s ausgehend und 32 GByte/s eingehend möglich. Neben Verbindungen zur North- und Southbridge können so auch zwei Cell-Prozessoren direkt miteinander verbunden werden.

## 2 HPC Hardware

# 3 Die Lattice Boltzmann Methode für die Flachwassergleichung

Bei der Lattice Boltzmann Methode (LBM) handelt es sich um eine Ende der 1980er Jahre entwickelten Methode zur numerischen Strömungssimulation. Sie verbindet die stark vereinfachte Teilchen-Mikrodynamik der Lattice Gas Automaten mit der Boltzmannschen Transportgleichung. Dieses Kapitel faßt in erster Linie die mathematischen Ergebnisse der Ausführungen von Zhou [60] zusammen, die notwendig sind, um Flachwassersimulationen mit der Lattice Boltzmann Methode durchzuführen. Dort sind auch weitergehende Informationen zu finden. Es wird bewusst auf die mathematischen Hintergründe und Herleitungen verzichtet, da diese Arbeit die Anwendung der LBM mit Hinblick auf hardwareeffiziente Berechnungen behandelt.

Die Flachwassergleichungen können angewendet werden, wenn die horizontalen Ausmaße (Wellenlänge  $\lambda$ ) deutlich größer als die vertikalen (Wellenhöhe  $\Delta h$ ) sind, also

$$1 \gg \frac{\Delta h}{\lambda} \tag{3.1}$$

gilt. Da die Tiefenwirkung einer Strömung nach obiger Bedingung vernachlässigt werden kann, kann das Modell auf mathematischer Ebene einfach gehalten werden. Die wesentliche Größe des Flachwassermodells ist die Wasserhöhe  $h(\mathbf{x},t)$  eines Fluids zum Zeitpunkt t an der Stelle  $\mathbf{x}$ , aus der die zu errechnende Fluidoberfläche konstruiert werden kann. Die Höheninformationen einer zweidimensionalen Fluidoberfläche werden auch als Höhenfeld bezeichnet. Der Zustand dieses Fluids wird vollständig durch seine Momentangeschwindigkeiten  $u_i(\mathbf{x},t)$  in kartesischen Richtungen i an jeder Stelle  $\mathbf{x}$  zum Zeitpunkt t beschrieben.

Üblicherweise werden die Flachwassergleichungen in der Erhaltungsform

$$\frac{\partial}{\partial t}Q + \frac{\partial}{\partial x}F(Q) + \frac{\partial}{\partial y}G(Q) = 0$$

(3.2)

angegeben. Hierbei entspricht

$$Q = \begin{pmatrix} h \\ hu_x \\ hu_y \end{pmatrix} \tag{3.3}$$

dem Vektor der konservativen Variablen, also der Wasserhöhe und den Geschwindigkeiten. Die Funktionen

$$F = \begin{pmatrix} hu \\ hu_x^2 + \frac{1}{2}gh^2 \\ hu_x u_y \end{pmatrix}$$

(3.4)

und

$$G = \begin{pmatrix} hu_x \\ hu_x u_y \\ hu_y^2 + \frac{1}{2}gh^2 \end{pmatrix}$$

$$(3.5)$$

können als Fluß über ein Kontrollvolumen in die beiden Raumrichtungen interpretiert werden. Der Faktor g entspricht der Gravitationskonstante.

Diese Erhaltungsform beschreibt also die Situation, dass sich die zeitlichen Veränderungen des Fluids in Höhe und Geschwindigkeit in der Summe über alle Orte des Höhenfeldes gegenseitig aufheben. Für eine ausführlichere Darstellung dieser Gleichungen wird etwa auf die Arbeit von Geveler [16] verwiesen.

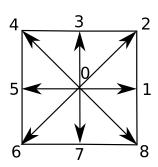

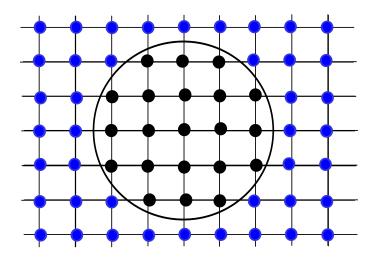

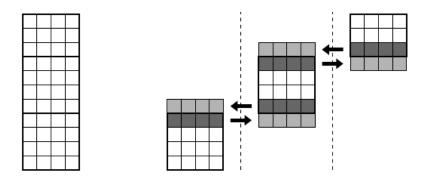

Dieses Flachwassermodell soll nun mit der Lattice Boltzmann Methode berechnet werden. Die grundlegende Idee der Lattice Boltzmann Methode ist die Simulation der Bewegung von fluiden Partikeln. Hierzu wird über das zu berechnende kontinuierliche Höhenfeld ein rechteckiges Gitter gelegt, um das Rechengebiet zu diskretisieren. Nun werden die auf dem Gitter liegenden Partikel in vorgegebene Richtungen von Gitterpunkt zu Gitterpunkt bewegt. Diese Richtungen werden durch die Struktur der Gitterzelle (Lattice) vorgegeben. Im Rahmen dieser Arbeit wird ein zweidimensionales Lattice mit neun vorgegebenen Richtungen  $\alpha \in (0, ..., 8)$  verwendet (D2Q9), wie es in Abbildung 3.1 zu sehen ist.

Abbildung 3.1: D2Q9 Lattice

Die Partikel können sich auf diesem Lattice in die Richtungen Eins bis Acht bewegen oder sich nicht bewegen (Richtung Null). Des weiteren gibt es zum Beispiel auch noch Lattices der Form D2Q5, D2Q7 oder im Dreidimensionalen ein Lattice der Form D3Q19.

Die Wechselwirkung der fluiden Partikel wird durch die folgende Lattice Boltzmann Gleichung beschrieben:

$$f_{\alpha}(\mathbf{x} + \mathbf{e}_{\alpha}\Delta t, t + \Delta t) - f_{\alpha}(\mathbf{x}, t) = -\frac{1}{\tau}(f_{\alpha} - f_{\alpha}^{eq})$$

(3.6)

Hierbei entspricht  $f_{\alpha}$  der zu errechnenden Verteilungsfunktion (Distributionsfunktion) in den neun Richtungen  $\alpha \in (0, ..., 8)$ .  $\tau$  stellt die Relaxationszeit dar, die durch einen Lösungsschritt berechnet wird. Der Geschwindigkeitsvektor  $\mathbf{e}_{\alpha}$  entspricht:

$$\mathbf{e}_{\alpha} = \begin{cases} (0,0) & \alpha = 0\\ e[\cos\frac{(\alpha-1)\pi}{4}, \sin\frac{(\alpha-1)\pi}{4}] & \alpha = 1,3,5,7\\ \sqrt{2}e[\cos\frac{(\alpha-1)\pi}{4}, \sin\frac{(\alpha-1)\pi}{4}] & \alpha = 2,4,6,8 \end{cases}$$

(3.7)

Die lokale Equilibriumverteilungs- oder Gleichgewichtsfunktion (equilibrium distribution)  $f_{\alpha}^{\text{eq}}$  bestimmt, welche Flußgleichung gelöst wird. Hier wird die folgende von Zhou [60] angegebene Funktion verwendet, um mit der LBM die Flachwassergleichung (3.2) zu berechnen. Die Funktion lautet:

$$f_{\alpha}^{\text{eq}} = \begin{cases} h - \frac{5gh^2}{6e^2} - \frac{2h}{3e^2} u_i u_i & \alpha = 0\\ \frac{gh^2}{6e^2} + \frac{h}{3e^2} e_{\alpha i} u_i + \frac{h}{2e^4} e_{\alpha j} u_i u_j - \frac{h}{6e^2} u_i u_i & \alpha = 1, 3, 5, 7\\ \frac{gh^2}{24e^2} + \frac{h}{12e^2} e_{\alpha i} u_i + \frac{h}{8e^4} e_{\alpha j} u_i u_j - \frac{h}{24e^2} u_i u_i & \alpha = 2, 4, 6, 8 \end{cases}$$

(3.8)

Hierbei fließen die wesentlichen Größe Wasserhöhe h und Momentangeschwindigkeiten  $u_i$  der Flachwassergleichung in die Funktion ein. Um später unnötige Berechnungen zu vermeiden, wird dieser Term vereinfacht, indem h nach Möglichkeit ausgeklammert wird:

$$f_{\alpha}^{\text{eq}} = \begin{cases} h(1 - \frac{5gh}{6e^2} - \frac{2}{3e^2}u_iu_i) & \alpha = 0\\ h(\frac{gh}{6e^2} + \frac{e_{\alpha i}u_i}{3e^2} + \frac{e_{\alpha j}u_iu_j}{2e^4} - \frac{u_iu_i}{6e^2}) & \alpha = 1, 3, 5, 7\\ h(\frac{gh}{24e^2} + \frac{e_{\alpha i}u_i}{12e^2} + \frac{e_{\alpha j}u_iu_j}{8e^4} - \frac{u_iu_i}{24e^2}) & \alpha = 2, 4, 6, 8 \end{cases}$$

$$(3.9)$$

Der Term  $-\frac{1}{\tau}(f_{\alpha} - f_{\alpha}^{\text{eq}})$  ist der Kollisionsoperator, der steuert, wie sich die Orientierung der Geschwindigkeiten ändert, wenn sich Partikel gegenseitig beeinflussen. Formt man die Lattice Boltzmann Gleichung (3.6) nach  $f_{\alpha}(\mathbf{x} + \mathbf{e}_{\alpha}\Delta t, t + \Delta t)$  um, so erhält man den Kollisions- und Strömungsschritt (collide and stream):

$$f_{\alpha}(\mathbf{x} + \mathbf{e}_{\alpha}\Delta t, t + \Delta t) = f_{\alpha}(\mathbf{x}, t) - \frac{1}{\tau}(f_{\alpha} - f_{\alpha}^{\text{eq}})$$

(3.10)

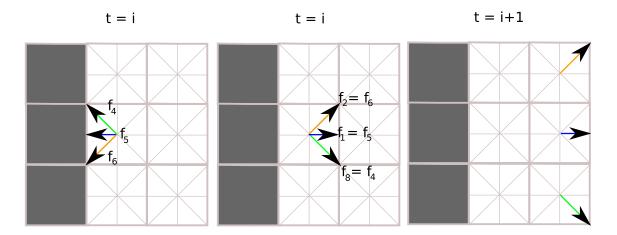

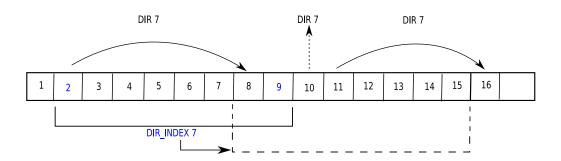

Wenn Partikel sich über den Rand des Rechengebietes hinausbewegen würden, müssen an diesen Rändern Korrekturen vorgenommen werden (update velocity directions). Die naheliegenste von Zhou angegebene Korrektur schlägt vor, Partikel, die einen Rand erreichen, an den gegenüberliegenden Rand zu transferieren und ihre Bewegungsrichtung beizubehalten. Dieses Verfahren nennt sich periodic boundary correction.

Ein komplizierteres Korrekturschema (no-slip boundary correction) lässt die Partikel, die einen Rand erreichen, von diesem reflektiert werden. Abbildung 3.2 zeigt ein Partikel, dass im Zeitschritt t=i den linken Rand des Rechengebiets erreicht. Um das Partikel zu reflektieren, werden nun seine nach links weisenden Distributionsfunktionen  $f_6$ ,  $f_5$  und

Abbildung 3.2: no-slip boundary correction

$f_4$  auf die nach rechts weisenden Distributionsfunktionen  $f_2$ ,  $f_1$ , und  $f_8$  kopiert, um die Bewegungsrichtung des Partikel umzukehren.

Allgemein kann diese Regel für Funktionen f in Richtung  $\beta$ , die in Richtung  $-\beta$  reflektiert werden, formuliert werden als

$$f_{-\beta} = f_{\beta} \tag{3.11}$$

$_{

m mit}$

$$-\beta = \begin{cases} \beta + 4, & 1 \le \beta \le 4 \\ \beta - 4, & 5 \le \beta \le 8. \end{cases}$$

(3.12)

Nachdem die Lattice Boltzmann Gleichung (3.6) gelöst und die Randbedingungen angewendet wurden, können die physikalischen Quantitäten extrahiert werden (extraction). Dies sind zum Einen die Wasserhöhe

$$h(\mathbf{x},t) = \sum_{\alpha} f_{\alpha}(\mathbf{x},t) \tag{3.13}$$

auf jedem Gitterpunkt und zum Anderen die Geschwindigkeitswerte in kartesischen Richtungen i:

$$u_i(\mathbf{x},t) = \frac{1}{h(\mathbf{x},t)} \sum_{\alpha} e_{\alpha i} f_{\alpha}$$

(3.14)

Ein kompletter Zeitschritt des Lattice Boltzmann Lösers besteht also aus den vier Teilschritten

- equilibrium distribution (Gleichung (3.9))

- collide and stream (Gleichung (3.10))

- update velocity directions (Randbehandlung)

- extraction (Gleichungen (3.13) und (3.14)).

Um korrekte Ergebnisse bei der Berechnung zu erhalten, ist es notwendig gewissen Anfangs- und Stabilitätsbedingungen zu genügen.

Zunächst sollten die physikalischen Quantitäten  $h(\mathbf{x},0)$  und  $u_i(\mathbf{x},0)$  initial vorgegeben werden, um mit ihnen initiale Gleichgewichtsfunktionen  $f_{\alpha}^{\text{eq}}$  berechnen zu können. Gleichzeitig müssen zu Beginn alle  $f_{\alpha}(\mathbf{x},0) \ \forall \alpha \in [0,8]$  auf 0 gesetzt werden.

Eine besondere Bedeutung kommt der Wahl korrekter Werte für die Zeitschrittweite  $\Delta t$  und die Relaxationszeit  $\tau$  zu. Durch die Methode und die verwendeten Flachwassergleichungen ergeben sich nach Zhou [60] hierzu einige Stabilitätsbedingungen. Zunächst entspricht die kinematische Viskosität  $\nu$  des D2Q9 Modells

$$\nu = \frac{e^2 \Delta t}{6} (2\tau - 1) > 0 \tag{3.15}$$

woraus sich direkt ergibt, dass

$$\tau > \frac{1}{2} \tag{3.16}$$

gelten muss. Zusätzlich beschränkt die Ausdehnung einer Gitterzelle die Geschwindigkeiten der Fluidpartikel durch

$$u_j u_j = e^2 (3.17)$$

und

$$gh = e^2. (3.18)$$

Zuletzt ergibt sich durch Gleichung (3.14), dass

$$h(\mathbf{x}, t) > 0 \tag{3.19}$$

gelten muss.

Da die Lattice Boltzmann Methode noch immer theoretisch erforscht wird und einige Stabilitätsbedingungen sich durch die gewählte Gleichgewichtsfunktion unterscheiden, garantiert das Einhalten der oben genannten Bedingungen nicht eine korrekte Berechung; es erleichtert lediglich die manuelle Wahl der korrekten Parameter, die sich von Szenario zu Szenario unterscheiden können.

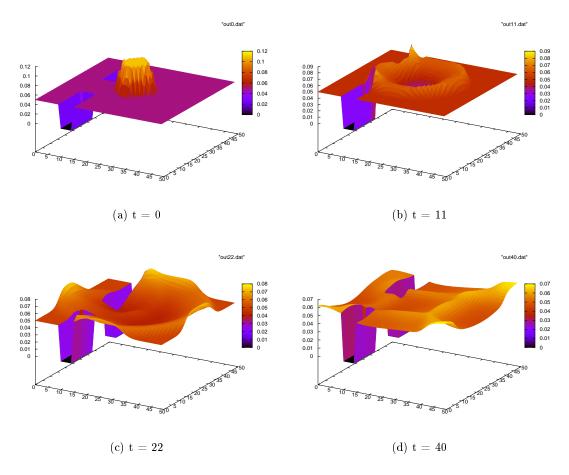

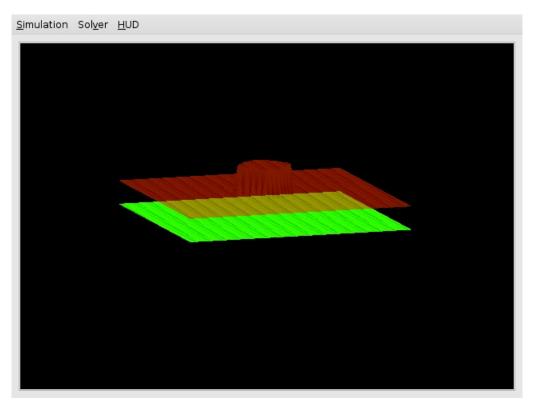

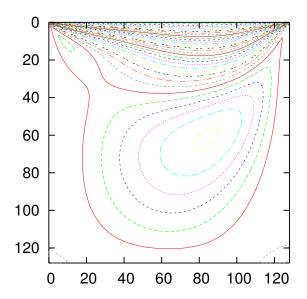

Abbildung 3.3 zeigt das Ergebnis einer tatsächlichen Berechnung des in Kapitel 5 vorgestellten LBM Lösers SolverLBMGrid auf einem quadratischen 100 × 100 Höhenfeld.

Hierbei ergießt sich eine initiale Wassersäule in ein Becken (zirkulärer Dammbruch), dass auf der linken oberen Seite durch eine Wand mit einem kleinen Durchgang in der Mitte begrenzt ist. Da die Zellen, die die Wände enthalten kein Wasser enthalten, entspricht dort die Wasserhöhe dem Wert Null. Man sieht also das Negativ der eigentlichen Wand. In Zeitschritt 11 ist das Wasser auf die Wand getroffen und fließt gleichzeitig durch den Durchgang in der Wand hindurch. In Zeitschritt 22 trifft das Wasser sowohl hinter dem Durchgang als auch auf allen anderen drei Seiten gegen die äußere Wand. Im letzten hier gezeigten Zeitschritt wurde das Wasser von allen Wänden zuruckgeworfen und beginnt, sich langsam zu beruhigen.

Abbildung 3.3: Flachwassersimmulation mit der LBM

## 4 HONEI

## 4.1 Übersicht

HONEI (hardware-oriented numerics efficiently implemented) ist eine Sammlung von Softwarebibliotheken, die einen einheitlichen Zugang für verschiedene Anwendungen aus dem Bereich des wissenschaftlichen Rechnen auf verschiedenen Hardwarearchitekturen ermöglichen. Mit der Entwicklung von HONEI wurde ursprünglich im Rahmen der Projektgruppe 512 "SmartCell: Clevere Algorithmen für den Cell Prozessor" [42] an den Fakultäten Informatik und Mathematik der TU Dortmund begonnen. Die wichtigsten Grundideen wurden bereits in einem Artikel unter Mitwirken des Autors der vorliegenden Arbeit [11] veröffentlicht.

Im Laufe der Projektgruppe stellte sich heraus, dass der anfängliche Ansatz, eine breite Hardwareunterstützung durch Bereitstellen von stark optimierten Basisoperationen aus der numerischen linearen Algebra, aus denen dann komplexere Anwendungen erstellt werden können, nicht in der Lage war, der darauf basierenden Anwendung einen hinreichend direkten Zugang zur jeweilige Hardware zu ermöglichen. Nur durch Kenntnis der Berechnungen und des Datenflusses über die gesamte Anwendung können insbesondere redundante Speicher- und Rechenoperationen vermieden und Datenzugriffsmuster gewählt werden, die die Speicherhierachie des Systems optimal ausnutzen. So mag eine stark vereinfachte Anwendung um a = a + b \* c zu berechnen zunächst ein Produkt r = b \* c berechnen, das Ergebnis speichern und in einem zweiten Schritt das Ergebnis wieder laden und die Summe a=r+c berechnen. Das Schreiben des Zwischenergebnisses r in den Speicher durch die erste Operation und das direkt im Anschluss durchgeführte erneute Laden von r durch die zweite Operation können vermieden werden, indem man die beiden Operationen zu einer komplexeren zusammenfasst. Dies ist insbesondere bei Architekturen, die keine schnellen Caches besitzen, sinnvoll, wie etwa der Cell BE oder einer Grafikkarte, aber selbst bei einer normalen CPU bringt der vorhandene Cache keinen Nutzen, wenn man sich die obigen Berechnungen als Vektoroperationen vorstellt und die Vektorgrößen als ein Vielfaches der Cachegröße annimmt.

Um dies zu ermöglichen wurde in HONEI das Konzept des Anwendungskernels eingeführt. Ein solcher Kernel fasst jeweils einen wesentlichen Teil der Berechnungen einer Anwendung zusammen und ermöglicht so die Optimierung weit über Operationsgrenzen hinweg. Gleichzeitig stellt der Kernel den kleinstmöglichen Teil der Anwendung dar, der

#### 4 HONEI

für jede Hardware reimplementiert und optimiert werden muss. Das eigentliche Anwendungsgerüst ruft dann diese Kernel auf und muss deshalb nicht für jede Hardware reimplementiert werden. Der Großteil von HONEI ist in C++ implementiert und nutzt sehr stark das in C++ vorhandene Template-Konzept und aus der Standard Template Library (STL) [48] bekannten Konzepte, wie zum Beispiel Iteratoren. Um die Anpassung an das jeweilige Zielsystem zu vereinfachen und den Erstellungsprozess der Bibliotheken zu automatisieren, kommt das GNU configure and build system (Autotools) [7] zum Einsatz. Insbesondere das skriptbasierte Erstellen der SPE Programme des Cell Backends macht hiervon sehr starken Gebrauch.

## 4.2 HONEI Komponenten

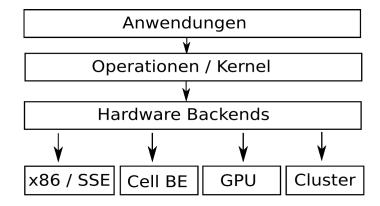

HONEI besteht aus einer Reihe von Bibliotheken, die aufeinander aufbauen und dadurch verschiedene Grade der Hardwareabstraktion erreichen. Abbildung 4.1 zeigt die schematische Struktur von HONEI. Auf unterster Ebene wird die direkte Schnittstelle zur jeweiligen

Abbildung 4.1: Struktur der HONEI Bibliotheken mit steigender Hardwarenähe von oben nach unten

Hardware durch die sogenannten Hardware Backends hergestellt. Das sind Bibliotheken, die die einzelnen Funktionen der entsprechenden Hardware zur Verfügung stellen, indem sie die vom jeweiligen Hardwarehersteller gelieferten Bibliotheken und hardwarespezifische Spracherweiterungen und Befehle nutzen. Auf diese setzen die Operationen und Kernel der restlichen anwendungsspezifischen Bibliotheken auf. Die Anwendungen wiederum setzen sich aus diesen Operationen und Kerneln zusammen. Durch diesen hierachischen Aufbau kann bei der Anwendungsentwicklung sehr stark von der Hardware abstrahiert entwickelt werden, während über die Operationen bis hin zu den Hardware Backends die Entwicklung immmer hardwarenäher wird.

Die nachfolgenden Abschnitte, deren Namen direkt HONEI entnommen wurden, beschreiben die HONEI Bibliotheken im Detail.

## 4.2.1 Util

Diese Bibliothek enthält Werkzeuge, die von allen anderen Bibliotheken verwendet werden können.

#### **Partitionierer**

Der Partitionierer wird dazu verwendet um beispielsweise einen Vektor in kleinere Teile zu zerlegen. Auf diese Weise können die erzeugten Teilvektoren auf verschiedenen Kernen einer CPU parallel bearbeitet oder über verschiedene Knoten eines Clusters verteilt werden. Um auf die verschiedenen Bedürfnisse der einzelnen Hardwarearchitekturen eingehen zu können, lassen sich eine Vielzahl von Parametern wie das Alignment der verschiedenen Partitionen, das heißt die Position der Daten im Speicher, die Anzahl der Partitionen und die minimale und maximale Partitionsgröße einstellen.

#### **Profiler**

Der Profiler kann eingesetzt werden, um detailierte Messungen der Ausführungszeit einzelner Programmabschnitte durchzuführen. Hierzu wurde eine einheitliche Schnittstelle entwickelt, die die verschiedenen hardwarespezifischen Techniken und Verfahren kapselt, gleichzeitig aber deren besondere Genauigkeit beibehält. Um Ausführungszeiten auf der CPU zu messen, kommt die Methode gettimeofday zum Einsatz, die die aktuelle Systemzeit in Mikrosekunden ausgibt. Allerdings ist die Auflösung nicht festgelegt und hängt von der verwendeten Systemuhr ab. Sie liegt gewöhnlich bei etwa einer Millisekunde und ist damit für detaillierte Messungen sehr ungenau. Auf einer SPE der Cell BE wird die Methode spu\_read\_decrementer genutzt, um die Ausführungszeit von dort ausgeführten Programmteilen zu messen. Diese gibt den Stand eines Zählers aus, der mit jedem Rechentakt um eins erniedrigt wird und ist somit sehr genau. Die Ausführungszeit auf der Grafikkarte wird mit der Methode cudaEventElapsedTime als verstrichene Zeit zwischen zwei vorher durch den Profiler erzeugten Ereignissen gemessen und liefert eine Auflösung von zirka  $0,5~\mu$ s. So kann zum Beispiel über die normalen Mittel des Anwendungsprogrammierers hinaus genau gemessen werden, wie lange Programmteile auf der Grafikkarte oder einer SPE ausgeführt werden.

## Debug

Die Klassen Log, Exception und Assertion ermöglichen eine einheitliche Fehlerverfolgung und Erkennung. Hierbei entsprechen Exception (Ausnahme) und Assertion (Zusicherung) in weiten Teilen ihren bekannten Pendanten aus C++. Sie wurden allerdings so erweitert, dass sie mit einem sogenannten Kontextstack zusammenarbeiten. Im Quelltext können Sinnabschnitte durch das CONTEXT Schlüsselwort markiert werden, die dann während der Pro-

#### 4 HONEI

grammausführung erkannt werden. Auf diese Weise kann eine ausgelöste Ausnahme oder eine verletzte Zusicherung direkt anzeigen, auf welchem Wege im Programmfluß (stacktrace) sie erreicht wurde. Zum Beispiel werden so zur Laufzeit Fehler wie ungenügende Ressourcen oder invalide Containergrößen erkannt und lokalisiert. Gleichzeitig können zur Fehlersuche detaillierte Informationen zum Beispiel über Datentransfers zwischen SPE und PPE des Cell Prozessors ausgegeben werden. Dazu genügt es, das LOGMESSAGE Schlüsselwort zu verwenden, um beliebige zum entsprechenden Zeitpunkt dem Programm zur Verfügung stehende Daten auszugeben. Die Klasse Log sorgt nun dafür, dass diese Daten auf dem Bildschirm oder in eine Datei ausgegeben werden. Um die Fehlersuche bei mehreren ausgeführten Threads zu erleichtern, wird diese Ausgabe mit der laufenden Nummer des Threads und dem oben angesprochenen Kontextstack ausgegeben. Im Falle von Systemen mit verteiltem Speicher, sorgt die Klasse Log ebenfalls dafür, dass die relevanten Daten automatisch aus dem Speicher der Grafikkarte oder einer SPE mit Hilfe des jeweiligen Hardware Backends in den Hauptspeicher transferiert werden, da sie nur von dort aus ausgegeben werden können.

#### **Thread**

Die Klassen Thread, Lock, Mutex und ConditionVariable stellen eine einheitliche Schnittstelle da, um nebenläufige Programmstukturen zu erzeugen. Sie basieren in erster Linie auf den sogenannten PThreads [4] und werden in erster Linie vom Multicore Backend aber auch vom Cell Backend eingesetzt. Hierbei stellt die Klasse Thread eine einfache Möglichkeit zur Verfügung, eine dem Konstruktor übergebene Methode als eigenständigen Thread auszuführen und wieder zu beenden. Die Klasse Lock ermöglicht es mehreren Threads sich zu synchronisieren, indem ein Thread den Zugriff auf eine Ressource für alle anderen Threads sperren kann bis er selbst die Ressource wieder freigibt. Um eine Quelle von Verklemmungen, sogenannten Deadlocks, zwischen Threads zu vermeiden, zerstört sich eine solche Sperre nach Beenden der jeweiligen Methode selbst und gibt die Ressource wieder frei; so muss der Programmierer dies nicht manuell zu tun. Die Klasse ConditionVariable ermöglicht es schließlich einer Menge von Threads ohne ständiges aktives Abfragen einer Statusinformation auf ein Ereignis zu warten und erst wieder aktiv zu werden, wenn das Ereignis eingetreten ist. Auf diese Weise können beispielsweise SPEs der CELL BE oder einzelne Kerne einer Multicore CPU warten (idle), bis ihnen neue Arbeit zugeteilt wird, ohne das System durch aktive Anfragen (polling, busy waiting) zu belasten.

## **TypeTraits**

Durch die TypeTraits sind die grundsätzlichen Operationen auf Datentypen implementiert. Dabei handelt es sich in erster Linie um optimierte Allokation, Deallokation, Kopier- und Verschiebeoperationen, die sich sowohl die Eigenarten der jeweiligen Hardware zu Nutze

machen, als auch auf die Eigenarten der jeweiligen Hardware eingehen, also zum Beispiel nur an sinnvollen Addressgrenzen ausgerichteten Speicher allokieren.

## **Memory Arbiter**

Der Memory Arbiter verwaltet Speicherorte und Zugriffe. Er wird als Neuentwicklung im Rahmen dieser Arbeit genauer in Abschnitt 4.3.1 beschrieben.

## 4.2.2 Hardware Backends

Um die für jeweilige Zielarchitektur effizient und hardwarenah programmmieren zu können, ist es meist unumgänglich, die gewünschten Funktionen in einer hardwarespezifischen Sprache zu formulieren und den jeweiligen Algorithmus an die Hardware anzupassen. Aus diesem Grund sind die optimierten Operationen und Kernel zusammen mit den Steuerund Kontrollbibliotheken in einzelnen Hardware Backends gekapselt.

## SSE

Das SSE Backend nutzt die von Intel zusammen mit den jeweiligen SSE Versionen entwickelten Intrinsics [28], um die SSE Register und Recheneinheiten direkt zu programmieren. Durch die verhältnismässig hohe Maschinennähe wird es möglich, Speicherzugriffe zu optimieren und die vorhandenen Register optimal auszunutzen. Da das durch eine Operation zu lösende Problem bekannt ist, können durch manuelle Optimierung bessere Ergebnisse erreicht werden, als dies die automatische Compileroptimierung zu leisten vermag.

Diese Intrinsics sind neue Schlüsselworte, die alle gängigen C++ Compiler unterstützen. Listing 4.1 zeigt die Operation a = a + b \* c auf drei Vektoren mit je vier Elementen. Zunächst werden je vier Elemente des Vektors b in m1 und vier Elemente des Vektors c in

```

float * a = {0, 1, 2, 3};

float * b = {0.0, 0.1, 0.2, 0.3};

float * c = {1.0, 1.1, 1.2, 1.3};

__m1 = _mm_load_ps(b);

m2 = _mm_load_ps(c);

m2 = _mm_mul_ps(m1, m2);

m1 = _mm_load_ps(a);

m1 = _mm_load_ps(a);

m1 = _mm_add_ps(m1, m2);

_mm_store_ps(a, m1);

```

Listing 4.1: SSE Intrinsics

m2 geladen. m1 und m2 stellen für den Compiler die SSE Register dar und sind 128 Byte groß, können also vier Variablen vom Typ float speichern. Dementsprechend steht das Suffix \_ps das den Intrinsics nachgestellt ist für packed single; sie rechnen also auf vier

#### 4 HONEI

Variablen mit einfacher Genauigkeit (single), die zusammen in einem Register gespeichert sind (packed). Das Prefix \_mm\_ ist historisch zu erklären und bezieht sich noch auf die erste von Intel entwickelte Vektorisierungstechnik MMX. Anschließend werden die vier Werte in m1 in einem Rechenschritt mit den vier Werten in m2 multipliziert und die Ergebnisse wieder in m2 gespeichert. Danach werden vier Elemente des Vektors a in m1 geladen und mit denen m2 addiert. Das in m1 gespeicherte Ergebnis wird schließlich zurück in den Vektor a geschrieben.

Da ein üblicher x86 Prozessor mindestens acht SSE Register besitzt, ist es bei größeren Vektoren üblich, soviele Elemente gleichzeitig zu verarbeiten, wie Registerplatz zur Verfügung steht. Im obigen Beispiel könnten die Befehle also vier Mal hintereinander auf verschiedenen Daten und Registern ausgeführt werden, um alle acht SSE Register zu nutzen. Eine Schleife auf diese Art abzurollen, wird loop unrolling genannt und kann den Gesamtdurchsatz der Operation stark erhöhen, da größere Datenblöcke gleichzeit transferiert und verarbeitet werden können.

#### Multicore

Das Multicore Backend baut auf den oben genannten Thread Klassen auf und ermöglicht eine effiziente Ausführung von Threads auf verschiedenen Kernen einer und mehrerer CPUs. Innerhalb dieser Threads können wiederum Operationen der anderen Backends ausgeführt werden. Eine übliche Anwendung ist zum Beispiel, auf mehreren Kernen Operationen des SSE Backends auszuführen. Es ist aber auch denkbar, mit geeigneter Hardware zwei Operationen des CUDA Backends parallel auf zwei Grafikkarten auszuführen. Hierbei kann mit Hilfe sogenannter "Threadaffinität" im Detail gesteuert werden, wo genau ein spezifischer Thread ausgeführt wird, um etwa Speicherzugriffe auf NUMA Architekturen zu optimieren. Gleichzeitig stellt die Verwendung eines Threadpools [36] sicher, dass auch bei kleineren Problemgrößen die Verwaltung der Threads die Ausführungszeit nicht wesentlich beeinflusst. Ein Threadpool verwaltet eine Menge von Threads, die dauerhaft existieren, aber nur aktiv werden, wenn sie das Signal (zum Beispiel durch eine ConditionVariable) bekommen, etwas zu berechnen. Ansonsten deaktivieren sie sich und beanspruchen keinerlei Ressourcen. Dadurch entfällt der ansonsten nötige Verwaltungsaufwand zur Erstellung und Zerstörung der einzelnen Threads. Zusätzlich werden Mittel geboten, um nicht blockierend auf die Ausführung der aufgegebenen Arbeit zu warten, sodass die Anwendung mit anderen Berechnungen fortfahren kann. Dies wird dadurch realisiert, dass die Anwendung zu jedem Zeitpunkt den Status der an das Multicore Backend delegierten Aufgaben erfragen kann und abhängig von diesem Status neue Aufgaben in Auftrag geben oder eigene davon unabhängige Berechnungen durchführen kann.

## **CUDA**

Das CUDA Backend bildet die Schnittstelle zwischen HONEI und einer mit CUDA programmierbaren Grafikkarte [35] Es wird genauer in Abschnitt 4.3.2 beschrieben.

## MPI

Das MPI Backend übernimmt die Organisation und Steuerung der MPI-gestützten Kommunikation und vereinfacht diese soweit wie möglich. Es wird genauer in Abschnitt 4.3.3 beschrieben.

## Cell

Da die grundsätzliche Programmierung der Cell BE deutlich aufwändiger ist, als etwa einen Algoritmus in SSE Intrinsics zu überführen, ist das Cell Backend deutlich umfangreicher als die anderen Hardware Backends. Zunächst muss auf Seite der PPE für jede einzusetzende SPE ein korrespondierender Thread gestartet werden. Diese sind wiederum dafür zuständig, die eigentlichen Programme auf den SPEs mit Hilfe der von IBM zur Verfügung gestellten Bibliothek libspe2 [26] und des IBM Cell BE SDK [41] zu starten. Um nicht für jede Operation erneut ein Programm auf einer SPE starten zu müssen, laufen dort dauerhaft sogenannte SPE Kernel, die je nach den an sie geschickten Instruktionen unterschiedliche Berechnungen ausführen. Ein Scheduler sorgt dafür, dass die einzelnen Instruktionen an freie SPEs versandt werden und dass dort ein Kernel ausgeführt wird, der diese Instruktion auch umsetzen kann. Den eigentlichen Datentransfer per DMA stößt dann die jeweilige SPE selbstständig an, da dies auf der Architektur für deutlich höhere Transferraten sorgt. Gleichzeitig kann die SPE Datentransfers und Berechnungen überlappen, indem sie durch sogenanntes double buffering auf einigen Daten rechnet, während die vorherigen Daten zurücktransferiert und die für die nächste Berechnung benötigten Daten hertransferiert werden. Um auch komplexere Aufgaben zu lösen, besteht für die SPEs die Möglichkeit DMA Listentransfers zu nutzen oder auch untereinander Daten auszutauschen.

Da wie weiter oben erwähnt eine SPE nur sehr wenig lokalen Speicher besitzt, in dem sowohl die Daten als auch die Instruktionen gespeichert werden müssen, enthält ein SPE Kernel immer nur Programmcode von einigen wenigen Operationen. Für verschiedene Anwendungen stehen deshalb verschiedene Kernel zur Verfügung, die exakt die notwendigen Operationen unterstützen, um ein notwendiges Austauschen der SPE Kernel auf den SPEs möglichst zu vermeiden. Um die Erstellung dieser Kernel zu vereinfachen, werden diese automatisch auf Basis einer einzelnen Textdatei erstellt, die die für den Kernel gewünschten Operationsnamen enthält. So steht maximal viel lokaler Speicher für die zu bearbeitenden Daten zur Verfügung.

Die eigentlichen auf der SPE ausgeführten Operationen sind schließlich in Intrinsics, ganz ähnlich denen, die zur SSE Programmierung zum Einsatz kommen, verfasst. Listing 4.2

zeigt den notwendigen SPE Quelltext, um die schon in Listing 4.1 behandelte Operation a = a + b \* c auf drei Vektoren mit je vier Elementen zu berechnen. Da durch das Cell

```

// DMA Transfer der Daten vom Hauptspeicher in den LS der SPE.

a = spu_madd(b, c, a);

// DMA Transfer der Daten vom LS der SPE in den Hauptspeicher.

```

Listing 4.2: Cell SPE Intrinsics

Backend vor Aufruf der Operation auf der SPE die notwendigen Daten in den Local Store der SPE und nach Abschluss der Operation wieder zurück in den Hauptspeicher transferiert werden, muss die Operation nur die eigentliche Berechnung durchführen. Da die SPE noch mehr als die SSE Einheit der CPU für die vektorisierte Bearbeitung von Daten optimiert ist, existiert die Operation a = a + b \* c direkt als Maschinenbefehl, der in einem Takt ausgeführt werden kann. Es ist also nicht notwendig, Addition und Multiplikation voneinander zu trennen.

#### 4.2.3 Unittest

Die Bibliothek zur Erzeugung von Unittests [22] stellt Werkzeuge zur Verfügung, um alle Container, Operationen, Kernel, Anwendungen und Bibliotheken von HONEI automatisiert auf korrekte Funktionsweise zu überprüfen. Hierdurch wird zum Einen die Entwicklung neuer Programmteile erleichtert, da die korrekte Funktionsweise direkt geprüft werden kann. Zum Anderen werden Softwareregressionen durch umfangreiche Regressionstests [58] erkannt und analysiert.

#### 4.2.4 Benchmark

Das Benchmark Framework ermöglicht eine einheitliche Erfassung und Analyse der Laufzeiten und Leistungsdaten von Operationen, Kerneln und Anwendungen auf allen genutzten Hardwarearchitekturen. Hierzu werden für alle Operationen und Kernel die durch sie ausgeführten Transfers und Fließkommaoperationen erfasst und akkumuliert. Somit entfällt beim Erstellen einer Anwendung eine aufwändige Analyse dieser Kennzahlen auf Anwendungsniveau. Gleichzeitig ermöglicht eine periodische Erfassung der Leistungsdaten aller HONEI Komponenten die direkte Identifikation negative Entwicklungen.

## 4.2.5 LA

Diese Bibliothek stellt eine Vielzahl von Containern und Operationen aus dem Bereich der linearen Algebra zur Verfügung und bildet damit die Grundlage aller anderen anwendungs-orientierten Bibliotheken.

### Container

Im Folgenden werden die in HONEI vorhandenen Container kurz aufgezählt. Allen Containern gemein ist, dass sie durch die Verwendung von Templates jeden gewünschten Datentyp speichern können; also zum Beispiel float, double, bool oder unsigned long. Zu beachten ist, dass eine echte datenunabhängige Kopie nur explizit über die Methode copy() erzeugt werden kann. In jedem anderen Fall werden nur die Containerobjekte kopiert, aber auf eine teure und häufig ungewollte Kopie aller Daten wird verzichtet. Außerdem stellen alle Container die Methoden lock() und unlock() zur Verfügung, um dem Memory Arbiter einen exklusiven Lese- oder Schreibzugriff zu signalisieren.

### Vektoren

- DenseVector: Gewöhnlicher Vektor, der als kontinuierliches eindimensionales Array seiner Elemente abgespeichert ist.

- SparseVector: Dieser Vektor enthält typischerweise nur wenige Nicht-Null-Elemente, die explizit mit ihren Positionen im Vektor gespeichert werden.

### Matrizen

- DenseMatrix: Gewöhnliche zweidimensionale Matrix, deren Elemente in einem eindimensionalen Array zeilenweise abgespeichert sind.

- SparseMatrix: Diese Matrix enthält typischerweise nur wenige Nicht-Null-Elemente, so dass ihre Zeilen jeweils als SparseVector abgespeichert werden können.

- SparseMatrixELL: Diese Matrix basiert auf dem ELLPACK Format, wie es in der ITPACK Bibliothek [20] vorgeschlagen wird. Hierbei werden die Nicht-Null-Elemente jeder Zeile zusammen mit ihrer jeweiligen Position in einer DenseMatrix gespeichert.

- BandedMatrix: Quadratische Bandmatrix. Hierbei werden die Daten in Form von Diagonalbändern als DenseVector abgespeichert.

- BandedMatrixQ1: Bandmatrix, die exakt neun diagonale Bänder an spezifischen Positionen enthält. Sie findet zum Beispiel Anwendung bei der Berechnung des Poisson Problems [11].

Die im Rahmen dieser Arbeit entwickelten LBM Löser verwenden ausschließlich die Container DenseVector und DenseMatrix.

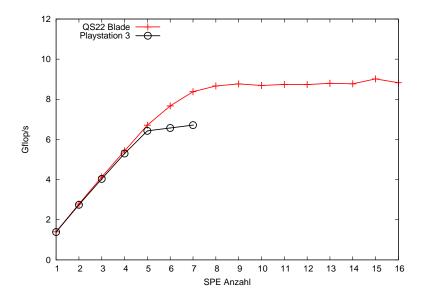

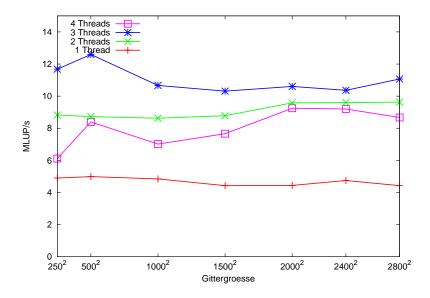

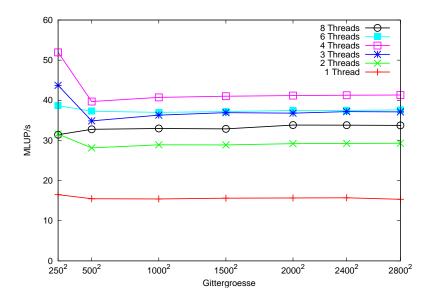

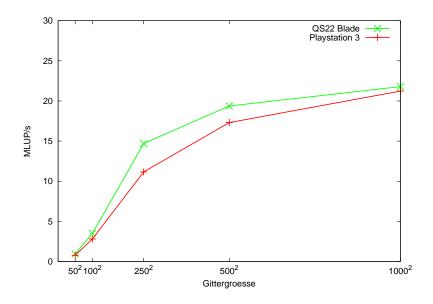

### Operationen